# PCI-DAS6013 & PCI-DAS6014

Analog and Digital I/O Boards

# **User's Guide**

# PCI-DAS6013 and PCI-DAS6014

Analog and Digital I/O

**User's Guide**

Document Revision 7, October, 2023 © Copyright 2023, Measurement Computing Corporation

#### **Trademark and Copyright Information**

Measurement Computing Corporation, InstaCal, Universal Library, and the Measurement Computing logo are either trademarks or registered trademarks of Measurement Computing Corporation. Refer to the Copyrights & Trademarks section on <u>mccdaq.com/legal</u> for more information about Measurement Computing trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies.

© 2023 Measurement Computing Corporation. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise without the prior written permission of Measurement Computing Corporation.

#### Notice

Measurement Computing Corporation does not authorize any Measurement Computing Corporation product for use in life support systems and/or devices without prior written consent from Measurement Computing Corporation. Life support devices/systems are devices or systems that, a) are intended for surgical implantation into the body, or b) support or sustain life and whose failure to perform can be reasonably expected to result in injury. Measurement Computing Corporation products are not designed with the components required, and are not subject to the testing required to ensure a level of reliability suitable for the treatment and diagnosis of people.

# Table of Contents

| Preface                                                                 | •      |

|-------------------------------------------------------------------------|--------|

| About this User's Guide                                                 |        |

| What you will learn from this user's guide                              |        |

| Conventions in this user's guide                                        |        |

| Where to find more information                                          | 6      |

| Chapter 1                                                               |        |

| Introducing the PCI-DAS6013 and PCI-DAS6014                             | 7      |

| Overview: PCI-DAS6013 and PCI-DAS6014 features                          | 7      |

| Software features                                                       | 7      |

| Chapter 2                                                               |        |

| Installing the PCI-DAS6013 and PCI-DAS6014                              | 8      |

| What comes with your PCI-DAS6013 and PCI-DAS6014 shipment?              |        |

| Hardware                                                                |        |

| Additional documentation                                                |        |

| Optional components                                                     |        |

| Unpacking the PCI-DAS6013 and PCI-DAS6014                               |        |

| Installing the software                                                 | 9      |

| Installing the hardware                                                 | 9      |

| Configuring the hardware                                                | 10     |

| Differential input mode                                                 |        |

| Single-ended input mode                                                 |        |

| Non-referenced single-ended input mode                                  |        |

| Connecting the board for I/O operations                                 |        |

| Connectors, cables – main I/O connector<br>Pin out – main I/O connector |        |

| Field wiring and signal termination                                     |        |

| Chapter 3                                                               |        |

| Functional Details                                                      | 16     |

| Basic architecture                                                      |        |

| Auxiliary input & output interface                                      |        |

| DAQ signal timing                                                       |        |

| SCANCLK signal                                                          |        |

| A/D START TRIGGER signal                                                |        |

| A/D STOP TRIGGER signal                                                 |        |

| STARTSCAN signalSSH signal                                              |        |

| A/D CONVERT signal                                                      |        |

| A/D PACER GATE signal                                                   | 22     |

| A/D EXTERNAL TIMEBASE signal                                            |        |

| A/D STOP signal                                                         |        |

| Waveform generation timing signals (PCI-DAS6014 only)                   |        |

| D/A START TRIGGER signal<br>D/A CONVERT signal                          |        |

| D/A CONVERT signal                                                      |        |

| General-purpose counter signal timing                                   |        |

| CTR1 CLK signal                                                         |        |

| CTR1 GATE signal                                                        |        |

| CTR1 OUT signal                                                         |        |

| CTR2 CLK signal                                                         |        |

| CTR2 GATE signal<br>CTR2 OUT signal                                     |        |

| erre eer signa                                                          | ······ |

| Chapter 4<br>Calibrating the Board                                                                        |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                              |    |

| Calibration theory                                                                                        |    |

| Chapter 5 Specifications                                                                                  | 30 |

| Analog input                                                                                              |    |

| Accuracy<br>System throughput<br>Settling time<br>Parametrics<br>Noise performance                        |    |

| Analog output (PCI-DAS6014 only)<br>Analog output pacing and triggering                                   |    |

| Analog input / output calibration                                                                         |    |

| Digital input / output                                                                                    |    |

| Interrupts                                                                                                |    |

| Counters                                                                                                  |    |

| Configurable AUXIN<5:0>, AUXOUT<2:0> external trigger/clocks                                              |    |

| Power consumption                                                                                         |    |

| Environmental                                                                                             |    |

| Mechanical                                                                                                |    |

| Main connector and pin out<br>8-channel differential mode pin out<br>16-channel single-ended mode pin out |    |

| Declaration of Conformity                                                                                 | 40 |

# About this User's Guide

## What you will learn from this user's guide

This user's guide explains how to install, configure, and use the PCI-DAS6013 and PCI-DAS6014 so that you get the most out analog input, analog output and digital I/O features.

This user's guide also refers you to related documents available on our web site, and to technical support resources that can also help you get the most out of these boards.

#### Conventions in this user's guide

#### For more information on ...

Text presented in a box signifies additional information and helpful hints related to the subject matter you are reading.

| Caution!           | Shaded caution statements present information to help you avoid injuring yourself and others, damaging your hardware, or losing your data.                                                                                                                                                   |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <#:#>              | Angle brackets that enclose numbers separated by a colon signify a range of numbers, such as those assigned to registers, bit settings, etc.                                                                                                                                                 |

| <b>bold</b> text   | <ul><li>Bold text is used for the names of objects on the screen, such as buttons, text boxes, and check boxes. For example:</li><li>1. Insert the disk or CD and click the OK button.</li></ul>                                                                                             |

| <i>italic</i> text | <i>Italic</i> text is used for the names of manuals and help topic titles, and to emphasize a word or phrase. For example:<br>The <i>InstaCal</i> installation procedure is explained in the Quick <i>Start Guide</i> .<br>Never touch the exposed pins or circuit connections on the board. |

## Where to find more information

For additional information relevant to the operation of your hardware, refer to the *Documents* subdirectory where you installed the MCC DAQ software (C:\Program Files\Measurement Computing\DAQ by default), or search for your device on our website at <u>www.mccdaq.com</u>.

If you need to program at the register level in your application, refer to the *STC Register Map for the PCI-DAS6000 Series*. This document is available at <u>www.mccdaq.com/registermaps/RegMapSTC6000.pdf</u>.

# Introducing the PCI-DAS6013 and PCI-DAS6014

## **Overview: PCI-DAS6013 and PCI-DAS6014 features**

This manual explains how to install and use the PCI-DAS6013 and PCI-DAS6014 analog and digital I/O boards.

These boards differ in that the PCI-DAS6014 has two digital-to-analog outputs, while the PCI-DAS6013 has no digital-to-analog outputs.

Both boards provide up to 16 analog inputs. Each input can be individually configured as single-ended or differential. The analog inputs have 16-bit resolution.

The boards' input ranges are bipolar-only. They have four ranges of  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 500mV$ , and  $\pm 50mV$ . The ranges are software-selectable.

The boards provide nine user-configurable trigger/clock/gate pins. They are available at a 100-pin I/O connector. Six are configurable as inputs and three are configurable as outputs.

Interrupts can be generated by up to seven ADC sources on both boards, and by up to four DAC sources on the PCI-DAS6014.

Each board contains an 82C54 counter chip, which consists of three 16-bit counters. Clock, gate, and output signals from two of the three counters are available on the 100-pin I/O connector. The third counter is used internally.

## **Software features**

For information on the features of *Insta*Cal and the other software included with your PCI-DAS6013 and PCI-DAS6014, refer to the *Quick Start Guide* that shipped with your device. The *Quick Start Guide* is also available in PDF at www.mccdaq.com/PDFmanuals/DAQ-Software-Quick-Start.pdf.

Check www.mccdaq.com/download.htm for the latest software version.

# Installing the PCI-DAS6013 and PCI-DAS6014

# What comes with your PCI-DAS6013 and PCI-DAS6014 shipment?

The following items are shipped with the PCI-DAS6013 and PCI-DAS6014.

#### Hardware

PCI-DAS6013 or PCI-DAS6014 board

PCI-DAS6013

#### Additional documentation

In addition to this hardware user's guide, you should also receive the *Quick Start Guide* (available in PDF at <u>www.mccdaq.com/PDFmanuals/DAQ-Software-Quick-Start.pdf</u>). This booklet supplies a brief description of the software you received with your PCI-DAS6013 and PCI-DAS6014 and information regarding installation of that software. Please read this booklet completely before installing any software or hardware.

#### **Optional components**

If you ordered any of the following products with your board, they should be included with your shipment.

Cables

C100HD50-x

C100MMS-x

Signal termination and conditioning accessories

MCC provides signal termination products for use with the PCI-DAS6013 and PCI-DAS6014. Refer to the "Field wiring, signal termination and conditioning" section on page 15 for a complete list of compatible accessory products.

# Unpacking the PCI-DAS6013 and PCI-DAS6014

As with any electronic device, you should take care while handling to avoid damage from static electricity. Before removing the PCI-DAS6013 and PCI-DAS6014 from its packaging, ground yourself using a wrist strap or by simply touching the computer chassis or other grounded object to eliminate any stored static charge.

If any components are missing or damaged, notify Measurement Computing Corporation immediately by phone, fax, or e-mail:

- Phone: 508-946-5100 and follow the instructions for reaching Tech Support.

- Fax: 508-946-9500 to the attention of Tech Support

- Email: <u>techsupport@mccdaq.com</u>

# Installing the software

Refer to the *Quick Start Guide* for instructions on installing the software on the *Measurement Computing Data Acquisition Software CD*. This booklet is available in PDF at <u>www.mccdaq.com/PDFmanuals/DAQ-Software-Quick-Start.pdf</u>.

## Installing the hardware

The PCI-DAS6013 and PCI-DAS6014 boards are completely plug-and-play. There are no switches or jumpers to set on the board. Configuration is controlled by your system's BIOS. To install your board, follow the steps below.

#### Install the MCC DAQ software before you install your board

The driver needed to run your board is installed with the MCC DAQ software. Therefore, you need to install the MCC DAQ software before you install your board. Refer to the *Quick Start Guide* for instructions on installing the software.

- 1. Turn your computer off, open it up, and insert your board into an available PCI slot.

- 2. Close your computer and turn it on.

If you are using an operating system with support for plug-and-play (such as Windows 2000 or Windows XP), a dialog box pops up as the system loads indicating that new hardware has been detected. If the information file for this board is not already loaded onto your PC, you will be prompted for the disk containing this file. The MCC DAQ software contains this file. If required, insert the *Measurement Computing Data Acquisition Software* CD and click **OK**.

**3.** To test your installation and configure your board, run the *Insta*Cal utility installed in the previous section. Refer to the *Quick Start Guide* that came with your board for information on how to initially set up and load *Insta*Cal.

Allow your computer to warm up for at least 15 minutes before acquiring data with these boards. The high speed components used on these boards generate heat and it takes this amount of time for a board to reach steady state if it has been powered off for a significant amount of time.

# Configuring the hardware

All hardware configuration options on the PCI-DAS6013 and PCI-DAS6014 are software controlled. You can select some of the configuration options using *Insta*Cal, such as digital channel configuration (input or output). Once selected, any program that uses the Universal Library initializes the hardware according to these selections.

Following is an overview of the available hardware configuration options for this board. There is additional general information regarding analog signal connection and configuration in the *Guide to Signal Connections* (available on our web site at <u>www.mccdaq.com/signals/signals.pdf</u>).

#### Differential input mode

When all channels are configured for differential input mode, eight analog input channels are available. In this mode, the input signal is measured with respect to the low input. The input signal is delivered through three wires:

- The wire carrying the signal to be measured connects to CH# IN HI.

- The wire carrying the reference signal connects to CH# IN LO.

- The third wire is connected to LLGND.

Differential input mode is the preferred configuration for applications in noisy environments, or when the signal source is referenced to a potential other than PC ground.

#### Single-ended input mode

When all channels are configured for single-ended input mode, 16 analog input channels are available. In this mode, the input signal is referenced to the board's signal ground (LLGND). The input signal is delivered through two wires:

- The wire carrying the signal to be measured connects to CH# IN HI.

- The other wire is connected to LLGND.

#### Non-referenced single-ended input mode

This mode is a compromise between differential and single-ended modes. It offers some of the advantages of each mode. With non-referenced single-ended mode, you can still get noise rejection, but not the limited number of channels resulting from a fully differential configuration. A possible downside is that the external reference input must be the same for every channel. It is equivalent to configuring the inputs for differential mode, tying all of the low inputs together, and using that node as the reference input.

When configured for non-referenced single-ended input mode, 16 analog input channels are available. In this mode, each input signal is referenced to a common reference signal (AISENSE), and not to the board's ground. The input signal is delivered through three wires:

- The wire carrying the signal to measure connects to CH# IN HI.

- The wire carrying the reference signal connects to AISENSE.

- The third wire is connected to LLGND.

This mode is useful when the application calls for differential input mode, but the limitation on channel count prevents it.

# Connecting the board for I/O operations

#### Connectors, cables - main I/O connector

The table below lists the board connectors, applicable cables, and compatible accessory products for the PCI-DAS6013 and PCI-DAS6014.

| Connector type                                           | Shielded, SCSI 100-pin D-type                                                                         |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

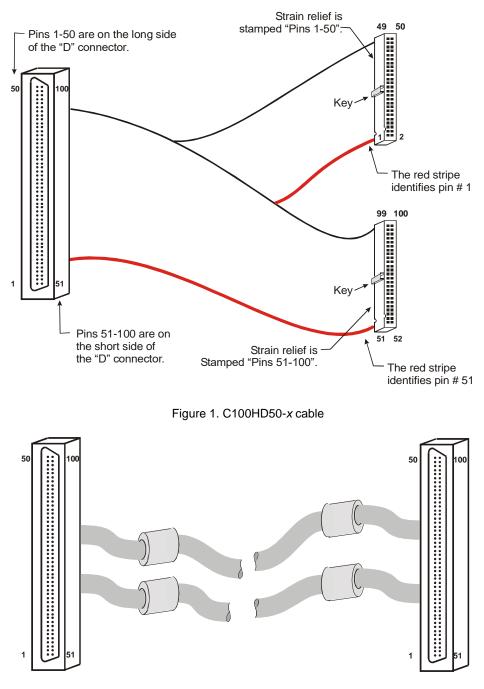

| Compatible cables                                        | C100HD50- <i>x</i> unshielded ribbon cable. $x = 3$ or 6 feet. (see Figure 1)                         |

|                                                          | C100MMS- <i>x</i> cable shielded round cable. $x = 1, 2, \text{ or } 3 \text{ meters}$ (see Figure 2) |

| Compatible accessory products                            | ISO-RACK16/P                                                                                          |

| (with the C100HD50-x cable)                              | ISO-DA02/P (PCI-DA6014 only)                                                                          |

|                                                          | BNC-16SE                                                                                              |

|                                                          | BNC-16DI                                                                                              |

|                                                          | CIO-MINI50                                                                                            |

|                                                          | CIO-TERM100                                                                                           |

|                                                          | SCB-50                                                                                                |

| Compatible accessory products (with the C100MMS-x cable) | SCB-100                                                                                               |

Board connectors, cables, and accessory equipment

|                             | Signal Name | Pin    |                                                                                                                                                    | Pin | Signal Name                |

|-----------------------------|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|

| Pin out – main I/O          | GND         | 100    | ſ                                                                                                                                                  | 50  | GND                        |

|                             | CTR2 OUT    | 99     | ••                                                                                                                                                 | 49  | AUXIN5 / A/D PACER GATE    |

| connector                   | CTR2 GATE   | 98     | ••                                                                                                                                                 | 48  | AUXIN4 / D/A START TRIGGER |

|                             | CTR2 CLK    | 97     | ••                                                                                                                                                 | 47  | AUXIN3 / D/A UPDATE        |

|                             | GND         | 96     | ••                                                                                                                                                 | 46  | AUXIN2 / A/D STOP TRIGGER  |

|                             | CTR1 OUT    | 95     | ••                                                                                                                                                 | 45  | AUXIN1 / A/D START TRIGGER |

|                             | CTR1 GATE   | 94     | ••                                                                                                                                                 | 44  | n/c                        |

| 8-channel differential mode | CTR1 CLK    | 93     | ••                                                                                                                                                 | 43  | AUXIN0 / A/D CONVERT       |

|                             | DIO7        | 92     | ••                                                                                                                                                 | 42  | AUXOUT2 / SCANCLK          |

|                             | DIO6        | 91     | ••                                                                                                                                                 | 41  | AUXOUT1 / A/D PACER OUT    |

|                             | DIO5        | 90     | ••                                                                                                                                                 | 40  | AUXOUT0 / D/A PACER OUT    |

| * N7 / 11 /1                | DIO4        | 89     | ••                                                                                                                                                 | 39  | PC +5 V                    |

| * Not available on the      | DIO3        | 88     | ••                                                                                                                                                 | 38  | D/A OUT1*                  |

| PCI-DAS6013                 | DIO2        | 87     | ••                                                                                                                                                 | 37  | D/A GND*                   |

|                             | DIO1        | 86     | ••                                                                                                                                                 | 36  | D/A OUT 0*                 |

|                             | DIO0        | 85     | ••                                                                                                                                                 | 35  | AISENSE                    |

|                             | n/c         | 84     | ••                                                                                                                                                 | 34  | n/c                        |

|                             | n/c         | 83     | ••                                                                                                                                                 | 33  | n/c                        |

|                             | n/c         | 82     | ••                                                                                                                                                 | 32  | n/c                        |

|                             | n/c         | 81     | ••                                                                                                                                                 | 31  | n/c                        |

|                             | n/c         | 80     | ••                                                                                                                                                 | 30  | n/c                        |

|                             | n/c         | 79     | ••                                                                                                                                                 | 29  | n/c                        |

|                             | n/c         | 78     | ••                                                                                                                                                 | 28  | n/c                        |

|                             | n/c         | 77     | ••                                                                                                                                                 | 27  | n/c                        |

|                             | n/c         | 76     | ••                                                                                                                                                 | 26  | n/c                        |

|                             | n/c         | 75     | ••                                                                                                                                                 | 25  | n/c                        |

|                             | n/c         | 74     | ••                                                                                                                                                 | 24  | n/c                        |

|                             | n/c         | 73     | ••                                                                                                                                                 | 23  | n/c                        |

|                             | n/c         | 72     | ••                                                                                                                                                 | 22  | n/c                        |

|                             | n/c         | 71     | ••                                                                                                                                                 | 21  | n/c                        |

|                             | n/c         | 70     | ••                                                                                                                                                 | 20  | n/c                        |

|                             | n/c         | 69     | ••                                                                                                                                                 | 19  | n/c                        |

|                             | n/c         | 68     | ••                                                                                                                                                 | 18  | LLGND                      |

|                             | n/c         | 67     | ••                                                                                                                                                 | 17  | CH7 IN LO                  |

|                             | n/c         | 66     | ••                                                                                                                                                 | 16  | CH7 IN HI                  |

|                             | n/c         | 65     | ••                                                                                                                                                 | 15  | CH6 IN LO                  |

|                             | n/c         | 64     | ••                                                                                                                                                 | 14  | CH6 IN HI                  |

|                             | n/c         | 63     | ••                                                                                                                                                 | 13  | CH5 IN LO                  |

|                             | n/c         | 62     | ••                                                                                                                                                 | 12  | CH5 IN HI                  |

|                             | n/c         | 61     | ••                                                                                                                                                 | 11  | CH4 IN LO                  |

|                             | n/c         | 60     | ••                                                                                                                                                 | 10  | CH4 IN HI                  |

|                             | n/c         | 59     | ••                                                                                                                                                 | 9   | CH3 IN LO                  |

|                             | n/c         | 58     | ••                                                                                                                                                 | 8   | CH3 IN HI                  |

|                             | n/c         | 57     | ••                                                                                                                                                 | 7   | CH2 IN LO                  |

|                             | n/c         | 56     | ••                                                                                                                                                 | 6   | CH2 IN HI                  |

|                             | n/c         | 55     | ••                                                                                                                                                 | 5   | CH1 IN LO                  |

|                             | n/c         | 54     | ••                                                                                                                                                 | 4   | CH1 IN HI                  |

|                             | n/c         | 53     | ••                                                                                                                                                 | 3   | CH0 IN LO                  |

|                             | n/c         | 52     | ••                                                                                                                                                 | 2   | CH0 IN HI                  |

|                             | n/c         | 51     | ••                                                                                                                                                 | 1   | LLGND                      |

|                             | POL         |        | $\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{$ |     |                            |

|                             | PCI         | slot ↓ |                                                                                                                                                    | J   |                            |

|                                       | Signal Name | Pin    |                 | Pin | Signal Name                |

|---------------------------------------|-------------|--------|-----------------|-----|----------------------------|

| 16-channel single-ended               | GND         | 100    | ĺ               | 50  | GND                        |

| mode                                  | CTR2 OUT    | 99     | ••              | 49  | AUXIN5 / A/D PACER GATE    |

| * Net merilelite en de e              | CTR2 GATE   | 98     | ••              | 48  | AUXIN4 / D/A START TRIGGER |

| * Not available on the<br>PCI-DAS6013 | CTR2 CLK    | 97     | ••              | 47  | AUXIN3 / D/A UPDATE        |

| PCI-DAS0013                           | GND         | 96     | ••              | 46  | AUXIN2 / A/D STOP TRIGGER  |

|                                       | CTR1 OUT    | 95     | ••              | 45  | AUXIN1 / A/D START TRIGGER |

|                                       | CTR1 GATE   | 94     | ••              | 44  | n/c                        |

|                                       | CTR1 CLK    | 93     | ••              | 43  | AUXIN0 / A/D CONVERT       |

|                                       | DIO7        | 92     | ••              | 42  | AUXOUT2 / SCANCLK          |

|                                       | DIO6        | 91     | ••              | 41  | AUXOUT1 / A/D PACER OUT    |

|                                       | DIO5        | 90     | ••              | 40  | AUXOUT0 / D/A PACER OUT    |

|                                       | DIO4        | 89     | ••              | 39  | PC +5 V                    |

|                                       | DIO3        | 88     | ••              | 38  | D/A OUT1*                  |

|                                       | DIO2        | 87     | ••              | 37  | D/A GND*                   |

|                                       | DIO1        | 86     | ••              | 36  | D/A OUT 0*                 |

|                                       | DIO0        | 85     | ••              | 35  | AISENSE                    |

|                                       | n/c         | 84     | ••              | 34  | n/c                        |

|                                       | n/c         | 83     | ••              | 33  | n/c                        |

|                                       | n/c         | 82     | ••              | 32  | n/c                        |

|                                       | n/c         | 81     | ••              | 31  | n/c                        |

|                                       | n/c         | 80     | ••              | 30  | n/c                        |

|                                       | n/c         | 79     | ••              | 29  | n/c                        |

|                                       | n/c         | 78     | ••              | 28  | n/c                        |

|                                       | n/c         | 77     | ••              | 27  | n/c                        |

|                                       | n/c         | 76     | ••              | 26  | n/c                        |

|                                       | n/c         | 75     | ••              | 25  | n/c                        |

|                                       | n/c         | 74     | ••              | 24  | n/c                        |

|                                       | n/c         | 73     | ••              | 23  | n/c                        |

|                                       | n/c         | 72     | ••              | 22  | n/c                        |

|                                       | n/c         | 71     | ••              | 21  | n/c                        |

|                                       | n/c         | 70     | ••              | 20  | n/c                        |

|                                       | n/c         | 69     | ••              | 19  | n/c                        |

|                                       | n/c         | 68     | ••              | 18  | LLGND                      |

|                                       | n/c         | 67     | ••              | 17  | CH15 IN                    |

|                                       | n/c         | 66     | ••              | 16  | CH7 IN                     |

|                                       | n/c         | 65     | ••              | 15  | CH14 IN                    |

|                                       | n/c         | 64     | ••              | 14  | CH6 IN                     |

|                                       | n/c         | 63     | ••              | 13  | CH13 IN                    |

|                                       | n/c         | 62     | ••              | 12  | CH5 IN                     |

|                                       | n/c         | 61     | ••              | 11  | CH12 IN                    |

|                                       | n/c         | 60     | ••              | 10  | CH4 IN                     |

|                                       | n/c         | 59     | ••              | 9   | CH11 IN                    |

|                                       | n/c         | 58     | ••              | 8   | CH3 IN                     |

|                                       | n/c         | 57     | ••              | 7   | CH10 IN                    |

|                                       | n/c         | 56     | ••              | 6   | CH2 IN                     |

|                                       | n/c         | 55     | ••              | 5   | CH9 IN                     |

|                                       | n/c         | 54     | ••              | 4   | CH1 IN                     |

|                                       | n/c         | 53     | ••              | 3   | CH8 IN                     |

|                                       | n/c         | 52     | ••              | 2   | CH0 IN                     |

|                                       | n/c         | 51     |                 | 1   | LLGND                      |

|                                       | PCI         | slot ↓ | $\overline{\ }$ | ļ   |                            |

Figure 2. C100MMS-x cable

Details on these cables are available on our web site at www.mccdaq.com/products/accessories.aspx.

#### Field wiring and signal termination

The following Measurement Computing accessory boards can be used with the PCI-DAS6013 and PCI-DAS6014:

#### Screw terminal boards and BNC adapters:

Use with the C100HD50-x cable:

- CIO-MINI50 50-pin universal screw terminal accessory.

- CIO-TERM100 16x4 screw terminal.

- SCB-50 50 conductor, shielded signal connection/screw terminal box provides two independent 50-pin connections.

Use with the C100MMS-x cable:

SCB-100 – 100 conductor, shielded signal connection/screw terminal box provides two independent 50-pin connections.

#### BNC connector boxes:

- BNC-16SE 16-channel single-ended BNC connector box.

- BNC-16DI Eight-channel differential BNC connector box.

Details on these products are available on our web site at <u>www.mccdaq.com/products/screw\_terminal\_bnc.aspx</u>.

#### ISO-5B module racks:

- ISO-RACK16/P 16-channel isolation module mounting rack.

- ISO-DA02/P (PCI-DA6014 only) Two-channel, 5B module rack.

Details on these products are available on our web site at <u>www.mccdaq.com/products/signal\_conditioning.aspx</u>.

# **Functional Details**

# **Basic architecture**

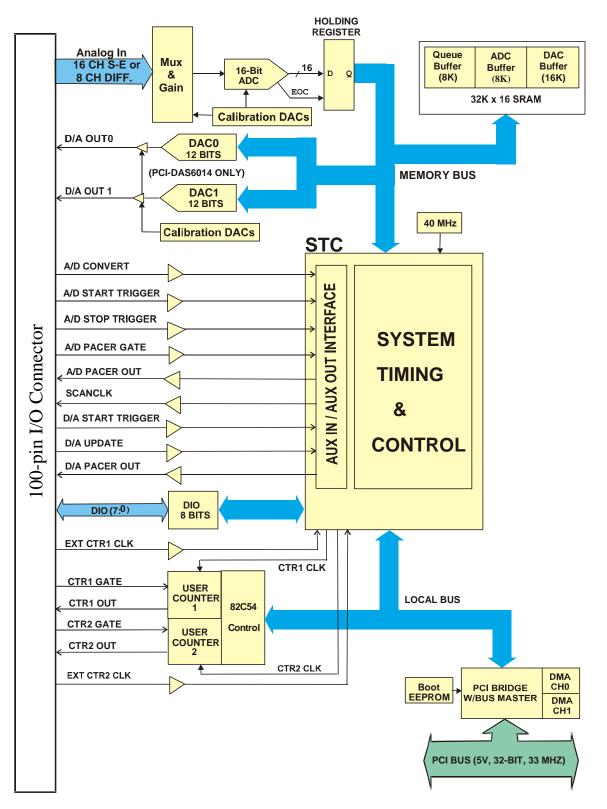

Figure 3 on page 18 shows a simplified block diagram of the PCI-DAS6013 and PCI-DAS6014. These boards provide all of the functional elements shown in the figure.

The System Timing and Control (STC) is the logical center for all DAQ, DIO, and DAC (if applicable) operations. It communicates over two major busses: a local bus and a memory bus.

The local bus carries digital I/O data and software commands from the PCI Bus Master. There are two Direct Memory Access (DMA) channels provided for data transfers to the PC.

Primarily, the memory bus carries A/D and D/A (PCI-DAS6014 only) related data and commands. There are three buffer memories provided on the memory bus:

- The *queue buffer* (8K configuration memory) stores programmed channel numbers, gains, and offsets.

- The *ADC buffer* (8K FIFO [First In, First Out]) temporarily stores scanned and converted analog inputs.

- The *DAC 16K buffer* stores data to be output as analog waveforms (this buffer function only applies to the PCI-DAS6014).

#### Auxiliary input & output interface

Each board's 100-pin I/O connector provides six software-selectable inputs, and three software-selectable outputs. The signals are user-configurable clocks, triggers and gates.

Refer to the "<u>DAQ signal timing</u>" section on page 19 for more explanation of these signals and their timing requirements.

The following table lists all of the possible and the default signals you use on the nine pins. D/A signals pertain only to the PCI-DAS6014.

| I/О Туре              | Signal Name          | Function                                                                     |  |  |

|-----------------------|----------------------|------------------------------------------------------------------------------|--|--|

| AUXIN<5:0> sources    | A/D CONVERT          | External ADC convert strobe (default)                                        |  |  |

| (software selectable) | A/D EXT. TIMEBASE IN | External ADC pacer time base                                                 |  |  |

|                       | A/D START TRIGGER    | ADC Start Trigger (default)                                                  |  |  |

|                       | A/D STOP TRIGGER     | ADC Stop Trigger (default)                                                   |  |  |

|                       | A/D PACER GATE       | External ADC gate (default)                                                  |  |  |

|                       | D/A START TRIGGER    | DAC trigger/gate (default) (PCI-DAS6014 only)                                |  |  |

|                       | D/A UPDATE           | DAC update strobe (default) (PCI-DAS6014 only)                               |  |  |

|                       | D/A EXT. TIMEBASE IN | External DAC pacer time base (PCI-DAS6014 only)                              |  |  |

| AUXOUT<2:0> sources   | STARTSCAN            | A pulse indicating the start of conversion.                                  |  |  |

| (software selectable) | SSH                  | An active signal that negates at the start of the last conversion in a scan. |  |  |

|                       | A/D STOP             | Indicates end of an acquisition sequence                                     |  |  |

|                       | A/D CONVERT          | ADC convert pulse (default)                                                  |  |  |

|                       | SCANCLK              | Delayed version of ADC convert (default)                                     |  |  |

|                       | CTR1 CLK             | CTR1 clock source                                                            |  |  |

|                       | D/A UPDATE           | D/A update pulse (default) (PCI-DAS6014 only)                                |  |  |

|                       | CTR2 CLK             | CTR2 clock source                                                            |  |  |

|                       | A/D START TRIGGER    | ADC Start Trigger Out                                                        |  |  |

|                       | A/D STOP TRIGGER     | ADC Stop Trigger Out                                                         |  |  |

|                       | D/A START TRIGGER    | DAC Start Trigger Out                                                        |  |  |

| Default selections    | AUXIN0:              | A/D CONVERT                                                                  |  |  |

| summary               | AUXIN1:              | A/D START TRIGGER                                                            |  |  |

|                       | AUXIN2:              | A/D STOP TRIGGER                                                             |  |  |

|                       | AUXIN3:              | D/A UPDATE (PCI-DAS6014 only)                                                |  |  |

|                       | AUXIN4:              | D/A START TRIGGER (PCI-DAS6014 only)                                         |  |  |

|                       | AUXIN5:              | A/D PACER GATE                                                               |  |  |

|                       | AUXOUT0:             | D/A UPDATE (PCI-DAS6014 only)                                                |  |  |

|                       | AUXOUT1:             | A/D CONVERT                                                                  |  |  |

|                       | AUXOUT2:             | SCANCLK                                                                      |  |  |

#### Auxiliary I/O Signals

Figure 3. Block diagram – PCI-DAS6013 and PCI-DAS6014

# **DAQ signal timing**

The DAQ timing signals are:

- SCANCLK

- A/D START TRIGGER

- A/D STOP TRIGGER

- STARTSCAN

- SSH

- A/D CONVERT

- A/D PACER GATE

- A/D EXTERNAL TIMEBASE

- A/D STOP

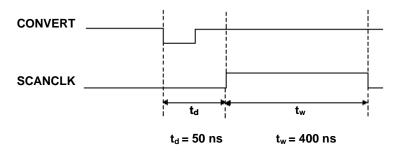

#### SCANCLK signal

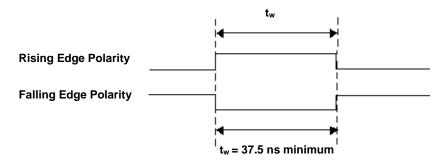

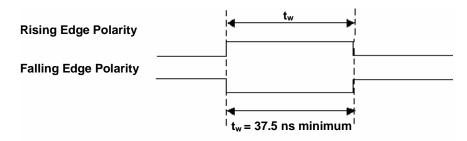

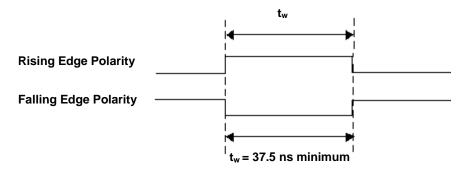

SCANCLK is an output signal that may be used for switching external multiplexers. It is a 400 ns wide pulse that follows the CONVERT signal after a 50 ns delay. This is adequate time for the analog input signal to be acquired so that the next signal may be switched in. The polarity of the SCANCLK signal is programmable. The default output pin for the SCANCLK signal is AUXOUT2, but any of the AUXOUT pins may be programmed as a SCANCLK output.

Figure 4. SCANCLK signal timing

#### A/D START TRIGGER signal

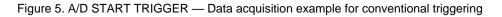

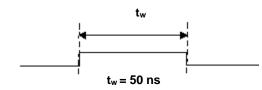

Use the A/D START TRIGGER signal for conventional triggering (when you only need to acquire data after a trigger event). Figure 5 shows the A/D START TRIGGER signal timing for a conventionally triggered acquisition.

| A/D Start Trigger<br>Start Scan |    |     |     |     |     |

|---------------------------------|----|-----|-----|-----|-----|

| Convert                         | ΨU | -ju | ļu— | -ju | -ju |

| Scan Counter                    | 4  | 3   | 2   | 1   | 0   |

The A/D START TRIGGER source is programmable and may be set to any of the AUXIN inputs. The polarity of this signal is also programmable to trigger acquisitions on either the positive or negative edge.

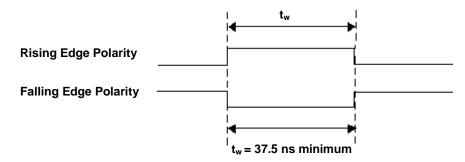

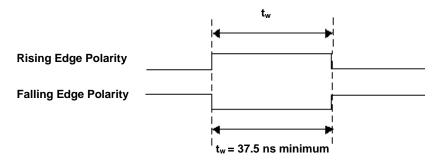

The A/D START TRIGGER signal is also available as an output and can be programmed to appear at any of the AUXOUT outputs. See Figure 6 and Figure 7 for A/D START TRIGGER input and output timing requirements.

Figure 6. A/D START TRIGGER input signal timing

Figure 7. A/D START TRIGGER output signal timing

The A/D START TRIGGER signal is also used to initiate pre-triggered DAQ operations (when you need to acquire data just before a trigger event). In most pre-triggered applications, the A/D START TRIGGER signal is generated by a software trigger. The use of A/D START TRIGGER and A/D STOP TRIGGER in pre-triggered DAQ applications is explained next.

#### A/D STOP TRIGGER signal

Pre-triggered data acquisition continually acquires data into a circular buffer until a specified number of samples have been collected after the trigger event. Figure 8 illustrates a typical pre-triggered DAQ sequence.

Figure 8. A/D STOP TRIGGER — Pre-triggered data acquisition example

The A/D STOP TRIGGER signal signifies when the circular buffer should stop and when the specified number of post trigger samples should be acquired. It is available as an output and an input. By default, it is available at AUXIN2 as an input but may be programmed for access at any of the AUXIN pins. It may be programmed for access at any of the AUXIN pins. It may be programmed for access at any of the AUXOUT pins as an output.

When using the A/D STOP TRIGGER signal as an input, the polarity may be configured for either rising or falling edge. The selected edge of the A/D STOP TRIGGER signal initiates the post-triggered phase of a pre-triggered acquisition sequence.

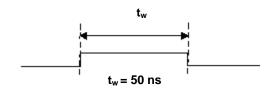

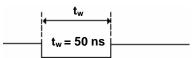

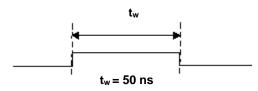

As an output, the A/D STOP TRIGGER signal indicates the event separating the pre-trigger data from the posttrigger data. The output is an active high pulse with a pulse width of 50 ns. Figure 9 and Figure 10 show the input and output timing requirements for the A/D STOP TRIGGER signal.

Figure 9. A/D STOP TRIGGER input signal timing

Figure 10. A/D STOP TRIGGER output signal timing

#### STARTSCAN signal

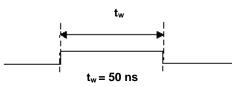

The STARTSCAN output signal indicates when a scan of channels has been initiated. You can program this signal to be available at any of the AUXOUT pins. The STARTSCAN output signal is a 50 ns wide pulse the leading edge of which indicates the start of a channel scan.

Figure 11. STARTSCAN start of scan timing

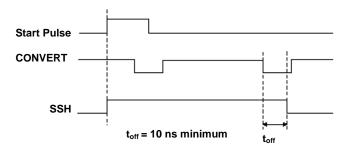

#### SSH signal

The SSH signal can be used as a control signal for external sample/hold circuits. The SSH signal is a programmable polarity pulse that is asserted throughout a channel scan. The state of this signal changes after the start of the last conversion in the scan. The SSH signal may be routed via software selection to any of the AUXOUT pins. Figure 12 shows the timing for the SSH signal.

Figure 12. SSH signal timing

#### A/D CONVERT signal

The A/D CONVERT signal indicates the start of an A/D conversion. It is available through software selection as an input to any of the AUXIN pins (defaulting to AUXIN0) and as an output to any of the AUXOUT pins.

When used as an input, the polarity is software selectable. The A/D CONVERT signal starts an acquisition on the selected edge. The convert pulses must be separated by a minimum of 5  $\mu$ s to remain within the 200 kS/s conversion rate specification.

Refer back to Figure 5 on page 19 and Figure 8 on page 20 for the relationship of A/D CONVERT to the DAQ sequence. Figure 13 and Figure 14 show the input and output pulse width requirements for the A/D CONVERT signal.

Figure 13. A/D CONVERT signal input timing requirement

Figure 14. A/D CONVERT signal output timing requirement

The A/D CONVERT signal is generated by the on-board pacer circuit unless the external clock option is in use. This signal may be gated by hardware (A/D PACER GATE) or software.

#### A/D PACER GATE signal

The A/D PACER GATE signal is used to disable scans temporarily. This signal may be programmed for input at any of the AUXIN pins.

If the A/D PACER GATE signal is active, no scans can occur. If the A/D PACER GATE signal becomes active during a scan in progress, the current scan is completed and scans are then held off until the gate is de-asserted.

#### A/D EXTERNAL TIMEBASE signal

You can use the A/D EXTERNAL TIMEBASE signal as the source for the on-board pacer circuit rather than the 40 MHz internal time base. Any AUXIN pin can be set programmatically as the source for this signal. The polarity is programmable.

The maximum frequency for the A/D EXTERNALTIMEBASE signal is 20 MHz. The minimum pulse width is 23 ns high or low. There is no minimum frequency specification.

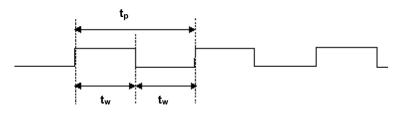

Figure 15 shows the timing specifications for the A/D EXTERNAL TIMEBASE signal.

t<sub>p</sub>=50 ns minimum

tw=23 ns minimum

Figure 15. A/D EXTERNAL TIMEBASE signal timing

#### A/D STOP signal

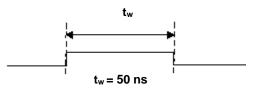

The A/D STOP signal indicates a completed acquisition sequence. You can program this signal to be available at any of the AUXOUT pins. The A/D STOP output signal is a 50 ns wide pulse whose leading edge indicates a DAQ done condition.

Figure 16. A/D STOP signal timing

# Waveform generation timing signals (PCI-DAS6014 only)

The signals that control the timing for the analog output functions on the PCI-DAS6014 are:

- D/A START TRIGGER

- D/A UPDATE

- D/A EXTERNAL TIME BASE

#### D/A START TRIGGER signal

The D/A START TRIGGER signal is used to hold off output scans until after a trigger event. Any AUXIN pin can be programmed to serve as the D/A START TRIGGER signal. It is also available as an output on any AUXOUT pin.

When used as an input, the D/A START TRIGGER signal may be software selected as either a positive or negative edge trigger. The selected edge of the D/A START TRIGGER signal causes the DACs to start generating the output waveform.

The D/A START TRIGGER signal can be used as an output to monitor the trigger that initiates waveform generation. The output is an active-high pulse having a width of 50 ns.

Figure 17 and Figure 18 show the input and output timing requirements for the D/A START TRIGGER signal.

Figure 17. D/A START TRIGGER input signal timing

Figure 18. D/A START TRIGGER output signal timing

### D/A CONVERT signal

The D/A CONVERT signal causes a single output update on the D/A converters. You can program any AUXIN pin to accept the D/A CONVERT signal. It is also available as an output on any AUXOUT pin.

The D/A CONVERT input signal polarity is software selectable. DAC outputs update within 100ns of the selected edge. The D/A CONVERT pulses should be no less than 100  $\mu$ s apart.

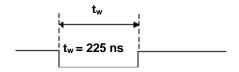

When used as an output, the D/A CONVERT signal may be used to monitor the pacing of the output updates. The output has a pulse width of 225 ns with selectable polarity.

The following figures show the input and output timing requirements for the D/A CONVERT signal.

Figure 19. D/A CONVERT input signal timing

Figure 20. D/A CONVERT output signal timing

#### D/A EXTERNAL TIMEBASE signal

The D/A EXTERNAL TIME BASE signal can serve as the source for the on-board DAC pacer circuit rather than using the internal time base. Any AUXIN pin can be set programmatically as the source for this signal. The polarity is programmable.

The maximum frequency for the D/A EXTERNAL TIMEBASE signal is 20 MHz. The minimum pulse width is 23 ns high or low. There is no minimum frequency specification.

Figure 21 shows the timing requirements for the D/A EXTERNAL TIMEBASE signal.

#### t<sub>p</sub> =50 ns minimum

Figure 21. D/A EXTERNAL TIMEBASE signal timing

#### General-purpose counter signal timing

The general-purpose counter signals are:

- CTR1 CLK

- CTR1 GATE

- CTR1 OUT

- CTR2 CLK

- CTR2 GATE

- CTR2 OUT

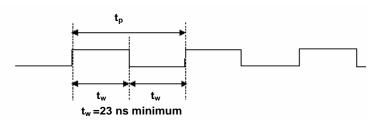

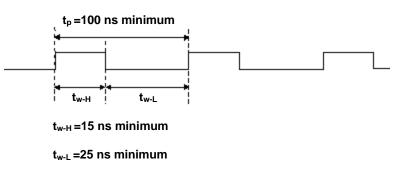

#### CTR1 CLK signal

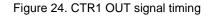

The CTR1 CLK signal can serve as the clock source for independent user counter 1. It can be selected through software at the CTR1 CLK pin rather than using the on-board 10 MHz or 100 kHz sources. It is also polarity programmable. The maximum input frequency is 10 MHz. There is no minimum frequency specified. Figure 22 shows the timing requirements for the CTR1 CLK signal.

#### CTR1 GATE signal

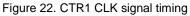

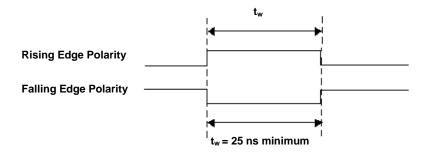

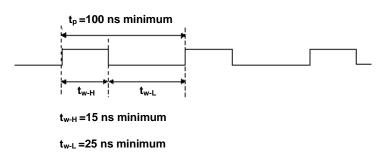

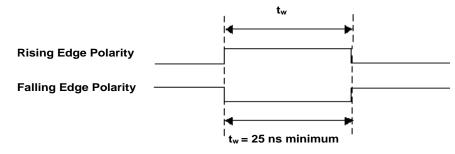

You can use the CTR1 GATE signal for starting and stopping the counter, saving counter contents, etc. It is polarity programmable and is available at the CTR1 GATE pin.

Figure 23 shows the minimum timing requirements for the CTR1 GATE signal.

Figure 23. CTR1 GATE signal timing

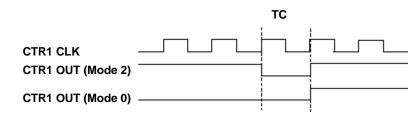

#### CTR1 OUT signal

This signal is present on the CTR1 OUT pin. The CTR1 OUT signal is the output of one of the two user's counters in an industry-standard 82C54 chip. Figure 24 shows the timing requirements for the CTR1 OUT signal for counter mode 0 and mode 2.

For detailed information on counter operations, please refer to the data sheet on our web site at <a href="http://www.mccdaq.com/PDFmanuals/82C54.pdf">www.mccdaq.com/PDFmanuals/82C54.pdf</a>.

#### CTR2 CLK signal

The CTR2 CLK signal can serve as the clock source for independent user counter 2. It can be selected through software at the CTR2 CLK pin rather than using the on-board 10 MHz or 100 kHz sources. It is also polarity programmable. The maximum input frequency is 10 MHz. There is no minimum frequency specified. Figure 25 shows the timing requirements for the CTR2 CLK signal.

Figure 25. CTR2 CLK signal timing

## CTR2 GATE signal

You can use the CTR2 GATE signal for starting and stopping the counter, saving counter contents, etc. It is polarity programmable and is available at the CTR2 GATE pin. Figure 26 shows the timing requirements for the CTR2 GATE signal.

Figure 26. CTR2 GATE signal timing

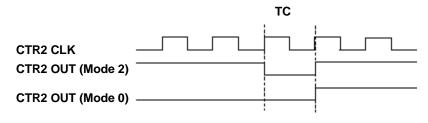

### CTR2 OUT signal

This signal is present on the CTR2 OUT pin. The CTR2 OUT signal is the output of one of the two user's counters in an industry-standard 82C54 chip. Figure 27 shows the timing of the CTR1 OUT signal for mode 0 and for mode 2.

For detailed information on counter operations, please refer to the data sheet on our web site at <a href="http://www.mccdaq.com/PDFmanuals/82C54.pdf">www.mccdaq.com/PDFmanuals/82C54.pdf</a>.

# **Calibrating the Board**

## Introduction

You should calibrate the board (using the *Insta*Cal utility) after the board has fully warmed up. The recommended warm-up time is 15 minutes. For best results, calibrate the board immediately before making critical measurements. The high resolution analog components on the board are somewhat sensitive to temperature. Pre-measurement calibration ensures that your board is operating at optimum calibration values.

## **Calibration theory**

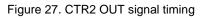

Analog inputs are calibrated for offset and gain. Offset calibration for the analog inputs is performed directly on the input amplifier, with coarse and fine trim DACs acting on the amplifier.

For input gain calibration, a precision calibration reference is used with coarse and fine trim DACs acting on the ADC (see Figure 28).

Figure 28. Analog input calibration - basic elements

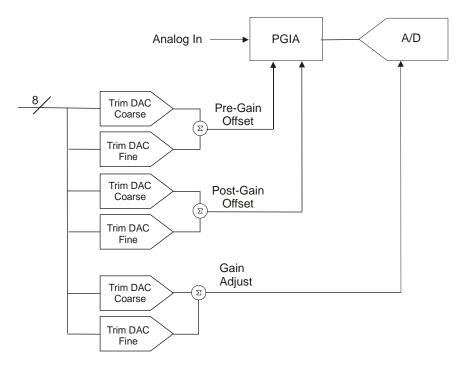

A similar method is used to calibrate the analog output components (PCI-DAS6014 only). A trim DAC is used to adjust the gain of the DAC. A separate DAC is used to adjust offset on the final output amplifier. The calibration circuits are duplicated for both analog outputs (see Figure 29).

Figure 29. Analog output calibration elements

# **Specifications**

#### Typical for 25 °C unless otherwise specified. Specifications in *italic text* are guaranteed by design.

# Analog input

| A/D converter                                           | Successive approximation type, min 200 kS/s conversion rate.                                            |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Resolution                                              | 16 bits, 1-in-65536                                                                                     |  |  |  |  |  |

| Number of channels                                      | 16 single-ended / 8 differential, software selectable                                                   |  |  |  |  |  |

| Input ranges                                            | $\pm 10 \text{ V}, \pm 5 \text{ V}, \pm 500 \text{ mV}, \pm 50 \text{ mV}, \text{ software selectable}$ |  |  |  |  |  |

| A/D pacing                                              | Internal counter – ASIC. Software selectable time base:                                                 |  |  |  |  |  |

|                                                         | <ul> <li>Internal 40 MHz, 50 ppm stability</li> </ul>                                                   |  |  |  |  |  |

|                                                         | <ul> <li>External source via AUXIN&lt;5:0&gt;, software selectable.</li> </ul>                          |  |  |  |  |  |

|                                                         | External convert strobe: A/D CONVERT                                                                    |  |  |  |  |  |

|                                                         | Software paced                                                                                          |  |  |  |  |  |

| Burst mode                                              | Software selectable option, burst rate = $5 \ \mu s$ .                                                  |  |  |  |  |  |

| A/D gate sources                                        | External digital: A/D GATE                                                                              |  |  |  |  |  |

| A/D gating modes                                        | External digital: Programmable, active high or active low, level or edge                                |  |  |  |  |  |

| A/D trigger sources External digital: A/D START TRIGGER |                                                                                                         |  |  |  |  |  |

|                                                         | A/D STOP TRIGGER                                                                                        |  |  |  |  |  |

| A/D triggering modes                                    | External digital: Software-configurable for rising or falling edge.                                     |  |  |  |  |  |

|                                                         | Pre-/post-trigger: Unlimited number of pre-trigger samples, 16 Meg post-trigger samples.                |  |  |  |  |  |

| ADC pacer out                                           | Available at user connector: A/D PACER OUT                                                              |  |  |  |  |  |

| RAM buffer size                                         | 8 K samples                                                                                             |  |  |  |  |  |

| Data transfer                                           | DMA                                                                                                     |  |  |  |  |  |

|                                                         | Programmed I/O                                                                                          |  |  |  |  |  |

| DMA modes                                               | Demand or non-demand using scatter gather.                                                              |  |  |  |  |  |

| Configuration memory                                    | Up to 8 K elements in the queue. Programmable channel, gain, and offset.                                |  |  |  |  |  |

| (see Note 1)                                            |                                                                                                         |  |  |  |  |  |

| Streaming-to-disk rate                                  | 200 kS/s, system dependent                                                                              |  |  |  |  |  |

|                                                         |                                                                                                         |  |  |  |  |  |

**Note 1:** Mixing high gains (±500 mV, ±50 mV) with low gains (±10 V, ±5 V) within the channel-gain queue is not supported.

# Accuracy

200 kS/s sampling rate, single channel operation and a 15-minute warm-up. Accuracies listed are for measurements made following an internal calibration. They are valid for operational temperatures within  $\pm 1$  °C of internal calibration temperature and  $\pm 10$  °C of factory calibration temperature. Calibrator test source high side tied to channel 0 high and low side tied to channel 0 low. Low-level ground is tied to channel 0 low at the user connector.

| Range   | Absolute Accuracy |

|---------|-------------------|

| ±10 V   | ±29.4 LSB         |

| ±5 V    | ±13.1 LSB         |

| ±500 mV | ±30.9 LSB         |

| ±50 mV  | ±45.2 LSB         |

| Range               | % of<br>Reading | Offset<br>(μV) | Averaged Noise +<br>Quantization (μV) <sup>1</sup> | Temp Drift (%/DegC) | Absolute<br>Accuracy at FS<br>(mV) |

|---------------------|-----------------|----------------|----------------------------------------------------|---------------------|------------------------------------|

| ±10 V               | 0.070           | 1800           | 180                                                | 0.001               | 8.984                              |

| ±5 V                | 0.020           | 918            | 85                                                 | 0.001               | 2.003                              |

| ±500 mV             | 0.070           | 109            | 12                                                 | 0.001               | 0.471                              |

| $\pm 50 \text{ mV}$ | 0.070           | 27             | 7                                                  | 0.001               | 0.069                              |

Table 2. Absolute accuracy components specifications - All values are (±)

<sup>1</sup> Averaged measurements assume averaging of 100 single-channel readings.

Each PCI-DAS6013 and PCI-DAS6014 is tested at the factory to assure the board's overall error does not exceed accuracy limits described in Table 1.

| All ranges       | ±0.5 LSB ty,p ±1.0 LSB max |  |

|------------------|----------------------------|--|

| No missing codes | 16 bits, guaranteed        |  |

#### System throughput

| Condition                                | Calibration Coefficients                         | ADC Rate (max) |

|------------------------------------------|--------------------------------------------------|----------------|

| 1. Single channel, single input range    | Per specified range                              | 200 kS/s       |

| 2. Multiple channel, single input range  | Per specified range                              | 200 kS/s       |

| 3. Single channel, multiple input ranges | Default to value for cbAInScan() range parameter | 200 kS/s       |

**Note 2:** For conditions 1-2 above, specified accuracy is maintained at rated throughput. Condition 3 applies a calibration coefficient which corresponds to the range value selected in cbAInScan(). This coefficient remains unchanged throughout the scan. Increased settling times may occur during gain-switching operations.

#### Settling time

Settling time is defined as the time required for a channel to settle to within a specified accuracy in response to a full-scale (FS) step. Two channels are scanned at the specified rate. A –FS DC signal is presented to channel 1; a +FS DC signal is presented to channel 0.

| Condition                | Range   | Accuracy   |            |

|--------------------------|---------|------------|------------|

|                          |         | ±0.0031%   | ±0.0062%   |

|                          |         | (±2.0 LSB) | (±4.0 LSB) |

| Same range to same range | ±10 V   | 5 µs typ   | *          |

|                          | ±5 V    | 5 µs max   | *          |

|                          | ±500 mV | 5 μs typ   | *          |

|                          | ±50 mV  | *          | 5 μs typ   |

#### **Parametrics**

| Max working voltage<br>(signal + common-mode) | ±11 V                                                  |  |  |

|-----------------------------------------------|--------------------------------------------------------|--|--|

| CMRR @ 60 Hz                                  | ±10 V range: 85 dB                                     |  |  |

|                                               | ±5 V range: 85 dB                                      |  |  |

|                                               | ±500 mV range: 93 dB                                   |  |  |

|                                               | ±50 mV range: 93 dB                                    |  |  |

| Small signal bandwidth, all ranges            | 425 kHz                                                |  |  |

| Input coupling                                | DC                                                     |  |  |

| Input impedance                               | 100 GOhm in normal operation.                          |  |  |

|                                               | 2 kOhm typ in powered off or overload condition.       |  |  |

| Input bias current                            | ±200 pA                                                |  |  |

| Input offset current                          | ±100 pA                                                |  |  |

| Absolute maximum input                        | ±25 V powered on, ±15 V powered off. Protected Inputs: |  |  |

| voltage                                       | <ul> <li>CH&lt;15:0&gt; IN</li> <li>AISENSE</li> </ul> |  |  |

| Crosstalk                                     | Adjacent channels: -75 dB                              |  |  |

|                                               | All other channels: -90 dB                             |  |  |

#### Noise performance

Table 4 summarizes the noise performance for the PCI-DAS6013 and PCI-DAS6014. Noise distribution is determined by gathering 50 K samples with inputs tied to ground at the user connector. Samples are gathered at the maximum specified single-channel-sampling rate. This specification applies to both single-ended and differential modes of operation.

| <b>-</b>                    | ,           |                |

|-----------------------------|-------------|----------------|

| Table 4. Analog input noise | performance | specifications |

| Range   | Typical Counts | LSBrms |

|---------|----------------|--------|

| ±10 V   | 7              | 1.2    |

| ±5 V    | 7              | 1.2    |

| ±500 mV | 11             | 2.0    |

| ±50 mV  | 45             | 6.7    |

# Analog output (PCI-DAS6014 only)

| D/A converter type                              | Double-buffered, multiplying        |  |  |

|-------------------------------------------------|-------------------------------------|--|--|

| Resolution                                      | 16 bits, 1-in-65536                 |  |  |

| Number of channels                              | 2 voltage output                    |  |  |

| Voltage range                                   | ±10 V                               |  |  |

| Monotonicity                                    | 16-bits, guaranteed monotonic       |  |  |

| DNL                                             | $\pm 2 LSB typ$                     |  |  |

| Slew rate                                       | 15 V/µs min                         |  |  |

| Settling time (full scale step)                 | 8 μs to ±1.0 LSB accuracy           |  |  |

| Noise                                           | 360 uVrms, DC to 400 kHz BW         |  |  |

| Glitch energy 200 mV @ 1 µs duration, mid-scale |                                     |  |  |

| Current drive                                   | ±5 mA                               |  |  |

| Output short-circuit duration                   | Indefinite @ 25 mA                  |  |  |

| Output coupling                                 | DC                                  |  |  |

| Output impedance                                | 0.1 ohms max                        |  |  |

| Power up and reset                              | DACs cleared to 0 volts ±250 mV max |  |  |

Г

٦

| Range                                                |  | Absolute Accuracy                                  |

|------------------------------------------------------|--|----------------------------------------------------|

| ±10 V ±                                              |  | ±12.6 LSB                                          |

| Table 6. Absolute accuracy components specifications |  | ble 6. Absolute accuracy components specifications |

| Table 5. Analog | g output at | osolute accurac | y specifications |

|-----------------|-------------|-----------------|------------------|

|-----------------|-------------|-----------------|------------------|

| Range | % of Reading<br>(1 year) | Offset<br>(mV) | Temp Drift<br>(%/DeqC) | Absolute Accuracy at FS (mV) |

|-------|--------------------------|----------------|------------------------|------------------------------|

|       |                          | · · /          | ,                      |                              |

| ±10 V | ±0.02                    | ±1.9           | ±0.0005                | ±3.84                        |

Each PCI-DAS6014 is tested at the factory to assure the board's overall error does not exceed the absolute accuracy specification listed in Table 5.

| Range | Relative Accuracy |

|-------|-------------------|

| ±10 V | ±3.0 LSB, typ     |

Relative accuracy is defined as the measured deviation from a straight line drawn between measured endpoints of the transfer function.

#### Analog output pacing and triggering

| DAC pacing              | Internal counter – ASIC. Selectable time base:                                 |  |  |

|-------------------------|--------------------------------------------------------------------------------|--|--|

| 1 0                     | <ul> <li>Internal 40 MHz, 50 ppm stability.</li> </ul>                         |  |  |

| (software programmable) | <ul> <li>External source via AUXIN&lt;5:0&gt;, software selectable.</li> </ul> |  |  |

|                         |                                                                                |  |  |

|                         | External convert strobe: D/A UPDATE                                            |  |  |

|                         | Software paced                                                                 |  |  |

| DAC gate source         | External digital: D/A START TRIGGER                                            |  |  |

| (software programmable) | Software gated                                                                 |  |  |

| DAC gating modes        | External digital: Programmable, active high or active low, level or edge       |  |  |

| DAC trigger sources     | External digital: D/A START TRIGGER                                            |  |  |

|                         | Software triggered                                                             |  |  |

| DAC triggering modes    | External digital: Software-configurable for rising or falling edge.            |  |  |

| DAC pacer out           | Available at user connector: D/A PACER OUT                                     |  |  |

| RAM buffer size         | 16 K samples                                                                   |  |  |

| Data transfer           | DMA                                                                            |  |  |

| Programmed I/O          |                                                                                |  |  |

|                         | Update DACs individually or simultaneously, software selectable.               |  |  |

| DMA modes               | Demand or non-demand using scatter gather.                                     |  |  |

| Waveform generation     | 10 kS/s max per channel, 2 channels simultaneous                               |  |  |