Multifunction Synchronous Data Acquisition Board

# **User's Guide**

# USB-1602HS-2AO

# Multifunction Synchronous Data Acquisition Board

**User's Guide**

Document Revision 3A, March, 2010 © Copyright 2010, Measurement Computing Corporation

### **Trademark and Copyright Information**

Measurement Computing Corporation, InstaCal, Universal Library, and the Measurement Computing logo are either trademarks or registered trademarks of Measurement Computing Corporation. Refer to the Copyrights & Trademarks section on <u>mccdaq.com/legal</u> for more information about Measurement Computing trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies.

© 2009 Measurement Computing Corporation. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise without the prior written permission of Measurement Computing Corporation.

#### Notice

Measurement Computing Corporation does not authorize any Measurement Computing Corporation product for use in life support systems and/or devices without prior written consent from Measurement Computing Corporation. Life support devices/systems are devices or systems that, a) are intended for surgical implantation into the body, or b) support or sustain life and whose failure to perform can be reasonably expected to result in injury. Measurement Computing Corporation products are not designed with the components required, and are not subject to the testing required to ensure a level of reliability suitable for the treatment and diagnosis of people.

# Table of Contents

| Preface<br>About this User's Guide                                                                     | 6  |

|--------------------------------------------------------------------------------------------------------|----|

| What you will learn from this user's guide                                                             | 6  |

| Conventions in this user's guide                                                                       | 6  |

| Where to find more information                                                                         | 6  |

| Chapter 1                                                                                              |    |

| Introducing the USB-1602HS-2AO                                                                         | 7  |

| Overview: USB-1602HS-2AO features                                                                      |    |

| Software features                                                                                      | 7  |

| Chapter 2<br>Installing the USB-1602HS-2AO                                                             |    |

| What comes with your USB-1602HS-2AO shipment?                                                          |    |

| Hardware<br>Optional components                                                                        |    |

| Additional documentation                                                                               |    |

| Signal conditioning accessories                                                                        |    |

| Unpacking the USB-1602HS-2AO                                                                           | 9  |

| Installing the software                                                                                |    |

| Installing the hardware                                                                                |    |

| Connecting the external power supply                                                                   |    |

| Connecting the USB-1602HS-2AO to your system                                                           |    |

| Configuring the USB-1602HS-2AO                                                                         |    |

| Connecting the board for I/O operations<br>Connectors, cables, and accessory products                  |    |

| Cabling                                                                                                |    |

| Field wiring and signal termination<br>TB-102 screw terminal board connector to SCSI connector pin out |    |

| -                                                                                                      | 13 |

| Chapter 3 Functional Details                                                                           |    |

| Front panel                                                                                            |    |

| BNC connectors                                                                                         |    |

| Status LEDs                                                                                            |    |

| Rear panel                                                                                             |    |

| SCSI connector<br>External power connector (EXT PWR)                                                   |    |

| USB connector                                                                                          |    |

| Analog common                                                                                          |    |

| Mechanical drawing                                                                                     |    |

| Block diagram                                                                                          | 16 |

| Synchronous analog, digital, and counter sampling                                                      |    |

| Input clock pacing                                                                                     |    |

| Output clock pacing                                                                                    |    |

| Analog inputs                                                                                          |    |

| Analog outputs                                                                                         |    |

| Digital I/O<br>Digital input scanning                                                                  |    |

| Internal pull-up/pull-down capability (J14)                                                            |    |

| Digital outputs and pattern generation                                                                 |    |

| Triggering                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware-based triggering<br>Software-based triggering                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |

| Stop trigger modes                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                  |

| Pre-triggering and post-triggering modes                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                  |

| Counter inputs                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |

| Mapped channels                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                                                                                                                                                                                                                               |

| Counter input modes<br>Debounce function                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                  |

| Quadrature detectors<br>Overview                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                  |

| Maximizing encoder accuracy                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |

| Connecting the USB-1602HS-2AO to an encoder                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |

| Timer/pulse generators                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                                                                                                                                                                                                                                               |

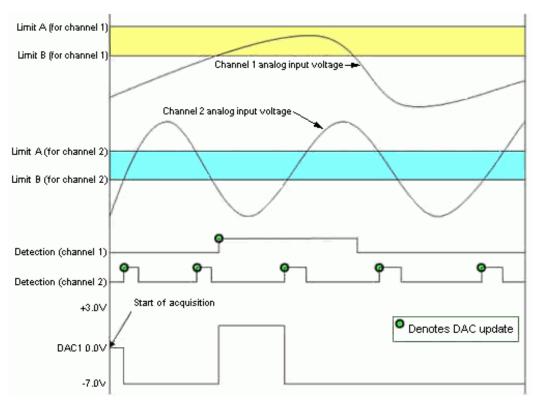

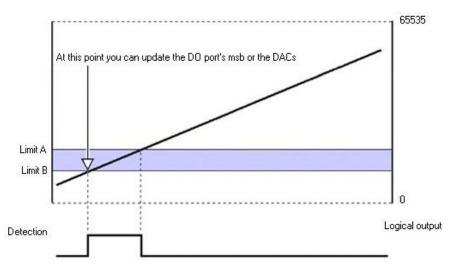

| Using detection setpoints for output control                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                  |

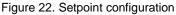

| Setpoint configuration                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |

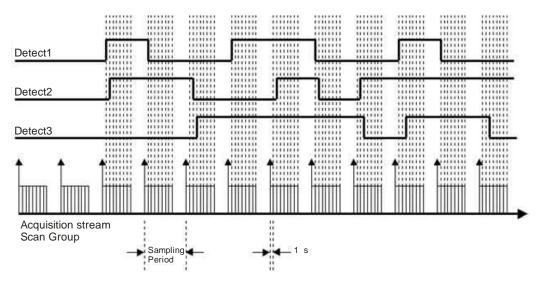

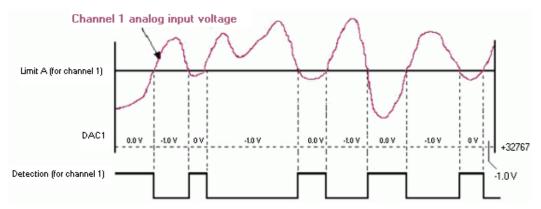

| Examples of control outputs<br>Controlling analog and digital outputs                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |

| Update latency                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |

| Using the setpoint status register                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                  |

| Chapter 4<br>Calibrating the USB-1602HS-2AO                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |

| Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |

| Specifications Analog input                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                  |

| Analog input                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters<br>Timers<br>Quadrature decoders<br>Power                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters<br>Timers<br>Quadrature decoders                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters<br>Timers<br>Quadrature decoders<br>Power                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters<br>Timers<br>Quadrature decoders<br>Power<br>USB specifications                                                                                                                                                                                                     | 37         38         39         39         39         39         40         41         42         42         43         43         43         43                                                                                                                                                |

| Analog input<br>Analog output<br>Analog input calibration<br>Digital inputs<br>Digital outputs<br>Trigger sources<br>Pacing sources<br>Counters<br>Timers<br>Quadrature decoders<br>Power<br>USB specifications<br>Environmental                                                                                                                                                                                    | 37         38         39         39         39         40         41         42         42         43         43         43         43         43         43         43         43         43         43         43         43                                                                   |

| Analog input         Analog output         Analog input calibration         Digital inputs         Digital outputs         Trigger sources         Pacing sources         Counters         Timers         Quadrature decoders         Power         USB specifications         Environmental         Mechanical                                                                                                     | 37         38         39         39         39         39         39         40         41         42         42         43         43         43         43         43         43         43         43         43         43         43         43         43         43         44         44 |

| Analog input         Analog output         Analog input calibration         Digital inputs         Digital outputs         Trigger sources         Pacing sources         Counters         Timers         Quadrature decoders         Power         USB specifications         Environmental         Mechanical         I/O cables, connectors and accessories         Signal I/O connectors         BNC connectors | 37         38         39         39         39         39         40         41         42         42         42         43         43         43         44         44         44         44                                                                                                    |

| Analog input         Analog output         Analog input calibration         Digital inputs         Digital outputs         Trigger sources         Pacing sources         Counters         Timers         Quadrature decoders         Power         USB specifications         Environmental         Mechanical         I/O cables, connectors and accessories         Signal I/O connectors                        | $\begin{array}{c} 37\\ 38\\ 39\\ 39\\ 39\\ 39\\ 39\\ 40\\ 41\\ 42\\ 42\\ 42\\ 43\\ 43\\ 43\\ 43\\ 43\\ 44\\ 44\\ 44\\ 44\\ 44$                                                                                                                                                                   |

# About this User's Guide

### What you will learn from this user's guide

This user's guide explains how to install, configure, and use the USB-1602HS-2AO so that you get the most out of its synchronous data acquisition features.

This user's guide also refers you to related documents available on our web site, and to technical support resources.

### Conventions in this user's guide

| For more information on |                                                                                                                                                                                                                                                                                      |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Text present reading.   | ted in a box signifies additional information and helpful hints related to the subject matter you are                                                                                                                                                                                |  |

| Caution!                | Shaded caution statements present information to help you avoid injuring yourself and others, damaging your hardware, or losing your data.                                                                                                                                           |  |

| <#:#>                   | Angle brackets that enclose numbers separated by a colon signify a range of numbers, such as those assigned to registers, bit settings, etc.                                                                                                                                         |  |

| <b>bold</b> text        | <ul><li>Bold text is used for the names of objects on the screen, such as buttons, text boxes, and check boxes. For example:</li><li>1. Insert the disk or CD and click the OK button.</li></ul>                                                                                     |  |

| <i>italic</i> text      | <i>Italic</i> text is used for the names of manuals and help topic titles, and to emphasize a word or phrase. For example:<br>The <i>InstaCal</i> installation procedure is explained in the Quick Start Guide.<br>Never touch the exposed pins or circuit connections on the board. |  |

### Where to find more information

For additional information relevant to the operation of your hardware, refer to the Documents subdirectory where you installed the MCC DAQ software (C:\Program Files\Measurement Computing\DAQ by default), or search for your device on our website at <u>www.mccdaq.com</u>.

# Introducing the USB-1602HS-2AO

### **Overview: USB-1602HS-2AO features**

The USB-1602HS-2AO is a multifunction high-speed measurement and control board supported under popular Microsoft<sup>®</sup> Windows<sup>®</sup> operating systems. The device is compatible with both USB 1.1 and USB 2.0 ports, (although the speed of the module maybe limited when using USB 1.1 ports).

The USB-1602HS-2AO provides the following features:

• Two single-ended 16-bit analog inputs, with one A/D converter per channel.

The maximum sampling rate is 2 MS/s per channel.

The input range is software programmable for  $\pm 10$  V,  $\pm 2.5$  V, or  $\pm 500$  mV.

- Two synchronous 16-bit ±10 V analog outputs can generate waveforms at 1 MS/s per channel.

- 16 synchronous digital inputs and 16 synchronous digital outputs

- Four 16-bit or 32-bit counters (can be configured to be gated)

- Two timer/pulse generators with pulse width (duty cycle) control

- Three 16-bit or 32-bit quadrature detectors to measure linear and rotary position

A 68-pin SCSI connector provides connections for all inputs and outputs except for the two analog inputs. Four BNC connectors provide connections for the two analog inputs, and alternate connections for the external pacer clock and external digital trigger input.

The USB-1602HS-2AO samples all analog inputs, digital inputs, and counter inputs simultaneously. You can synchronize AI, AO, and DIO operations at rates of up to 1 MS/s (million samples per second), with aggregate throughput up to 8 MS/s.

You can pace operations with an internal or external clock.

A 500 VDC isolation barrier between the field wiring and USB interface reduces signal noise and protects the board and your computer from ground spikes. The USB 2.0 high-speed driver transfers data at rates up to 480 Mbps.

The device is powered by a 10 Watt regulated external power supply that is included with shipment. Factory and self-calibration tables are stored onboard in EEPROM.

### **Software features**

For information on the features of *Insta*Cal and the other software included with your USB-1602HS-2AO, refer to the *Quick Start Guide* that shipped with your device.

# Installing the USB-1602HS-2AO

### What comes with your USB-1602HS-2AO shipment?

#### Hardware

USB-1602HS-2AO

• USB cable (2-meter length)

• External power supply and cord – 5 volts, 10 watt AC power adapter. MCC part number PS-5V2AEPS

### **Optional components**

#### Cables

- Standard BNC cable

- CA-68-3R cable

- CA-68-3S (3 foot shielded cable)

- CA-68-6S (6 foot shielded cable)

#### Screw termination board with screw terminals

• TB-102

### Additional documentation

In addition to this hardware user's guide, you should also receive the *Quick Start Guide* (available in PDF at <u>www.mccdaq.com/PDFmanuals/DAQ-Software-Quick-Start.pdf</u>). This booklet supplies a brief description of the software you received with your USB-1602HS-2AO and information regarding installation of that software. Please read this booklet completely before installing any software or hardware.

#### Signal conditioning accessories

MCC provides signal termination products for use with the USB-1602HS-2AO. Refer to the "Field wiring and signal termination" section for a complete list of compatible accessory products.

### Unpacking the USB-1602HS-2AO

As with any electronic device, take care while handling to avoid damage from static electricity. Before removing the USB-1602HS-2AO from its packaging, ground yourself using a wrist strap or by simply touching the computer chassis or other grounded object to eliminate any stored static charge.

If the USB-1602HS-2AO is damaged, notify Measurement Computing Corporation immediately by phone, fax, or e-mail.

- Phone: 508-946-5100 and follow the instructions for reaching Tech Support.

- Fax: 508-946-9500 to the attention of Tech Support

- Email: <u>techsupport@mccdaq.com</u>

For international customers, contact the local distributor where you purchased the USB-1602HS-2AO. Click on this link <u>www.measurementcomputing.com/sales.asp</u> to locate your distributor.

### Installing the software

Refer to the *Quick Start Guide* for instructions on installing the software on the *Measurement Computing Data Acquisition Software CD*. This booklet is available in PDF at <u>www.mccdaq.com/PDFmanuals/DAQ-Software-Quick-Start.pdf</u>.

### Installing the hardware

Power to the USB-1602HS-2AO is provided with the 10 watt AC power adapter (PS-5V2AEPS). The power supply ships with a U.S. plug. Optional interchangeable plugs for international locations are available.

#### Connecting the external power supply

Connect the AC power adapter cord to the **EXT. PWR** connector on the device's rear panel, and plug the adapter into an electrical outlet.

The **POWER** LED on the front panel turns on when the device is detected by the system.

#### Connect external power before connecting the USB cable to the computer

Connect the external power cable to the USB-1602HS-2AO before connecting the USB cable to the computer. This allows the USB-1602HS-2AO to inform the host computer (when the USB cable is connected) that the board requires minimal power from the computer's USB port.

#### Connecting the USB-1602HS-2AO to your system

To connect the USB-1602HS-2AO to your system, turn the computer on, and connect a USB cable from the **USB** connector on the rear panel to either a USB port on the computer or external USB hub connected to the computer.

When you connect the USB-1602HS-2AO for the first time, a **Found New Hardware** message opens as the device is detected. When the message closes, the installation is complete.

### Configuring the USB-1602HS-2AO

All hardware configuration options on the USB-1602HS-2AO are software controlled with the exception of the digital pull-up / pull-down (described below), which is set for pull-up by default. You can select some of the configuration options using *Insta*Cal, such as the analog input range and the trigger source. Once selected, any program that uses the Universal Library will initialize the hardware according to these selections.

### Connecting the board for I/O operations

#### Connectors, cables, and accessory products

The following table lists the board connectors, applicable cables, and compatible accessory products for the USB-1602HS-2AO.

| Parameter                                                                      | Specification                                                                                                                                       |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Connector types                                                                | <ul> <li>Four standard BNC female connectors for analog input, clock<br/>input, and digital trigger input</li> <li>68-pin SCSI connector</li> </ul> |

| Compatible cable for the BNC connectors                                        | Standard BNC cable                                                                                                                                  |

| Compatible cables for the 68-pin SCSI connector                                | <ul> <li>CA-68-3R</li> <li>CA-68-3S or CA-68-6S shielded cable</li> </ul>                                                                           |

| Compatible accessory products using the CA-68-3R, CA-68-3S, or CA-68-6S cables | TB-102 screw terminal board                                                                                                                         |

#### Board connectors, cables, and compatible hardware

#### **BNC** connectors

The USB-1602HS-2AO has four BNC connectors used to connect the analog input signals, external pacer clock input, and external digital trigger input.

Figure 1. BNC connectors

The signal names for the BNC connectors are listed below:

| BNC Label | Signal connection              |

|-----------|--------------------------------|

| CH0       | Analog input 0                 |

| CH1       | Analog input 1                 |

| EXT TRG   | External digital trigger input |

| EXT CLK   | External pacer clock input     |

EXT TRG is equivalent to the DIG TRIG signal on the SCSI connector. EXT CLK is equivalent to the XAPCR signal on the SCSI connector. Connect your signals using a standard BNC cable.

#### 68-pin SCSI connector

The signals that are available on the 68-pin SCSI connector are listed below.

| Signal name                         | Pin |     | Pin | Signal name                    |

|-------------------------------------|-----|-----|-----|--------------------------------|

| DGND                                | 68  | ••  | 34  | DGND                           |

| (external pacer clock output) XDPCR | 67  | ••  | 33  | CTR6 Z                         |

| (external pacer clock input) XAPCR  | 66  | ••  | 32  | CTR6 B                         |

| DIG TRIG                            | 65  | ••  | 31  | CTR6 A                         |

| TMR/PWM1                            | 64  | ••  | 30  | CTR5 Z                         |

| TMR/PWM0                            | 63  | ••  | 29  | CTR5 B                         |

| CTR3                                | 62  | ••  | 28  | CTR5 A                         |

| CTR2                                | 61  | ••  | 27  | CTR4 Z                         |

| CTR1                                | 60  | ••  | 26  | CTR4 B                         |

| CTR0                                | 59  | ••  | 25  | CTR4 A                         |

| DOUT15                              | 58  | ••  | 24  | DIN15                          |

| DOUT14                              | 57  | ••  | 23  | DIN14                          |

| DOUT13                              | 56  | ••  | 22  | DIN13                          |

| DOUT12                              | 55  | • • | 21  | DIN12                          |

| DOUT11                              | 54  | • • | 20  | DIN11                          |

| DOUT10                              | 53  | ••  | 19  | DIN10                          |

| DOUT9                               | 52  | • • | 18  | DIN9                           |

| DOUT8                               | 51  | • • | 17  | DIN8                           |

| DOUT7                               | 50  | • • | 16  | DIN7                           |

| DOUT6                               | 49  | ••  | 15  | DIN6                           |

| DOUT5                               | 48  | • • | 14  | DIN5                           |

| DOUT4                               | 47  | ••  | 13  | DIN4                           |

| DOUT3                               | 46  | ••  | 12  | DIN3                           |

| DOUT2                               | 45  | ••  | 11  | DIN2                           |

| DOUT1                               | 44  | ••  | 10  | DIN1                           |

| DOUT0                               | 43  | ••  | 9   | DINO                           |

| AGND                                | 42  | ••  | 8   | AGND                           |

| DAC 1                               | 41  | ••  | 7   | +5VPWR                         |

| DAC 0                               | 40  | ••  | 6   | VCAL (reserved for calibration |

| AGND                                | 39  | ••  | 5   | AGND                           |

| Reserved                            | 38  | ••  | 4   | Reserved                       |

| AGND                                | 37  | ••  | 3   | AGND                           |

| Reserved                            | 36  | ••  | 2   | Reserved                       |

| AGND                                | 35  | ••  | 1   | AGND                           |

Connect your signals using a CA-68-3R cable, or CA-68-3S or CA-68-6S shielded cable.

### Cabling

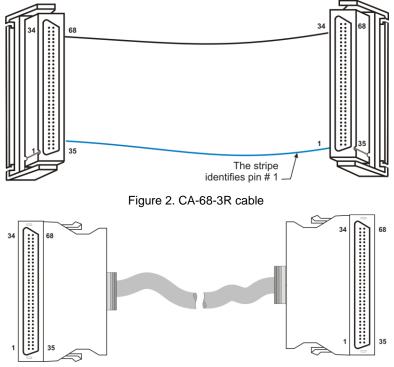

Use a CA-68-3R 68-pin ribbon expansion cable (Figure 2), or a CA-68-3S (3-foot) or CA-68-6S (6-foot) 68-pin shielded expansion cable (Figure 3) to connect signals to the USB-1602HS-2AO's 68-pin SCSI connector.

Figure 3. CA-68-3S and CA-68-6S shielded cable

Details on these cables are available at <u>www.mccdaq.com/usb-data-acquisition/USB-1604HS-2AO.aspx</u>.

### Field wiring and signal termination

You can use the following Measurement Computing screw terminal board to terminate field signals and route them into the USB-1602HS-2AO board using the CA-68-3R, CA-68-3S, or CA-68-6S cable:

• **TB-102**: Termination board with screw terminals. Details on this product are available on our web site at <u>www.mccdaq.com/products/screw terminal bnc.aspx</u>.

A 19-inch rack mount kit (**RM-TB-102**) for the TB-102 termination board is also available.

### TB-102 screw terminal board connector to SCSI connector pin out

The TB-102 terminal board is shown here. The table below lists how signals on the TB-102 are mapped to the signals on the 68-pin SCSI connector.

| TB1 screw terminals | SCSI<br>pin | TB2 screw<br>terminals | SCSI<br>pin |

|---------------------|-------------|------------------------|-------------|

| AGND                | 1           | AGND                   | 35          |

| Reserved            | 2           | Reserved               | 36          |

| AGND                | 3           | AGND                   | 37          |

| Reserved            | 4           | Reserved               | 38          |

| AGND                | 5           | AGND                   | 39          |

| VCAL                | 6           | DAC0                   | 40          |

| +5VOUT              | 7           | DAC1                   | 41          |

| AGND                | 8           | AGND                   | 42          |

| DIN0                | 9           | DOUT0                  | 43          |

| DIN1                | 10          | DOUT1                  | 44          |

| DIN2                | 11          | DOUT2                  | 45          |

| DIN3                | 12          | DOUT3                  | 46          |

| DIN4                | 13          | DOUT4                  | 47          |

| DIN5                | 14          | DOUT5                  | 48          |

| DIN6                | 15          | DOUT6                  | 49          |

| DIN7                | 16          | DOUT7                  | 50          |

| DIN8                | 17          | DOUT8                  | 51          |

| DIN9                | 18          | DOUT9                  | 52          |

| DIN10               | 19          | DOUT10                 | 53          |

| DIN11               | 20          | DOUT11                 | 54          |

| DIN12               | 21          | DOUT12                 | 55          |

| DIN13               | 22          | DOUT13                 | 56          |

| DIN14               | 23          | DOUT14                 | 57          |

| DIN15               | 24          | DOUT15                 | 58          |

| CTR4A               | 25          | CTR0                   | 59          |

| CTR4B               | 26          | CTR1                   | 60          |

| CTR4Z               | 27          | CTR2                   | 61          |

| CTR5A               | 28          | CTR3                   | 62          |

| CTR5B               | 29          | TMR/PWM0               | 63          |

| CTR5Z               | 30          | TMR/PWM1               | 64          |

| CTR6A               | 31          | DIGTRIG                | 65          |

| CTR6B               | 32          | XAPCR                  | 66          |

| CTR6Z               | 33          | XDPCR                  | 67          |

| DGND                | 34          | DGND                   | 68          |

| DGND                | *           | DGND                   | *           |

| EGND                | **          | EGND                   | **          |

Pin mapping between the TB-102 terminal board and the 68-pin SCSI connector

\* Extra digital ground connectors

\*\* EGND is connected to the SCSI connector shell.

# **Functional Details**

### Front panel

Figure 4. USB-1602HS-2AO front panel

#### **BNC** connectors

The USB-1602HS-2AO has four BNC connectors that provide connections for the following signals:

- Two single-ended analog inputs

- External digital trigger input

- External pacer clock input

These signals are also available on the 68-pin SCSI connector.

#### Status LEDs

The **POWER** LED lights up after the device is enumerated by the system. The **ACTIVE** LED lights up when the USB-1602HS-2AO is transmitting or receiving data.

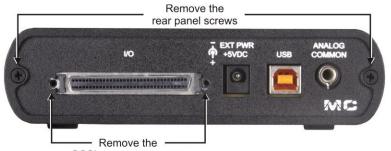

### **Rear panel**

Figure 5. USB-1602HS-2AO rear panel

#### **SCSI** connector

The 68-pin SCSI connector provides connections for all I/O signals except for analog input: Refer to page 12 for the connector pin out.

- Two analog outputs (DAC0 and DAC1)

- 16 digital inputs (DIN1 to DIN15)

- 16 digital outputs (DOUT1 to DOUT15)

- Four counters (CTR0 to CTR3). Two counters may be gated.

- Three quadrature detectors (CTR4 A, B, and Z to CTR6 A, B, and Z)

- Two timer/pulse outputs (TMR/PWM0 to TMR/PWM1)

- Digital trigger input (DIG TRIG)

- Input pacer clock (XAPCR)

- Output pacer clock (XDPCR)

- Analog ground (AGND)

- Digital ground (DGND)

- Calibration (VCAL)

- +5V PWR

### External power connector (EXT PWR)

The USB-1602HS-2AO requires external power. Connect the PS-5V2AEPS power supply to the EXT PWR connector. This power supply provides 5 VDC, 2 A power, and plugs into a standard 120 VAC outlet.

#### **USB** connector

The USB connector provides communication with the host PC.

#### Analog common

The analog ground reference for the analog inputs and analog outputs.

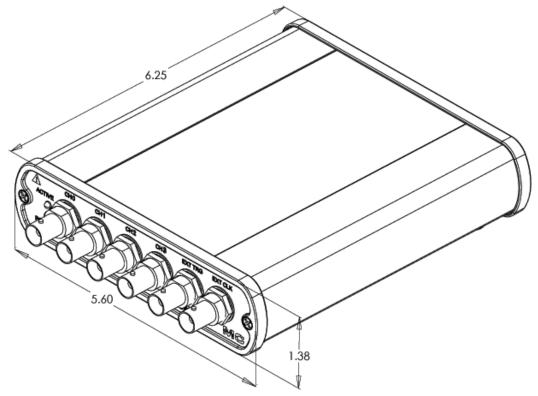

### **Mechanical drawing**

Figure 6. USB-1602HS-2AO case dimensions

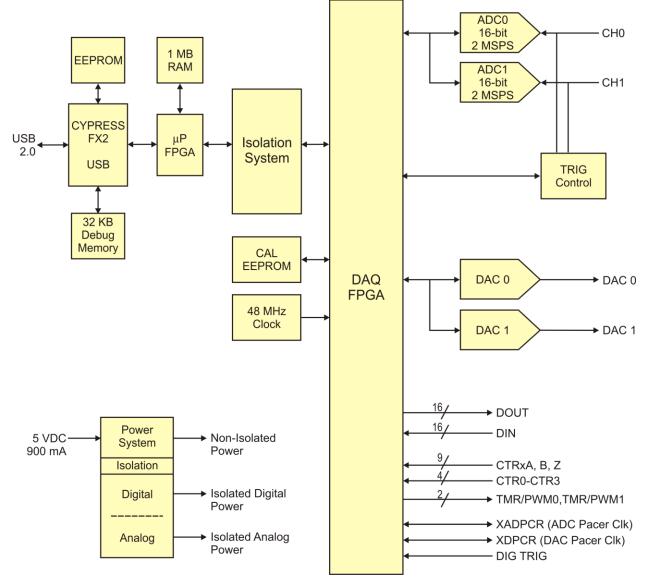

### **Block diagram**

USB-1602HS-2AO functions are illustrated in the block diagram shown here.

Figure 7. USB-1602HS-2AO functional block diagram

### Synchronous analog, digital, and counter sampling

The USB-1602HS-2AO samples all analog, digital, and counter inputs simultaneously, while also generating up to two analog outputs and digital pattern outputs at the same time.

The maximum analog input sampling rate is 2 MS/s. Digital channels (digital input and counter channels) can be sampled at rates up to 8 MS/s for one channel when no analog channels are sampled, and rates of up to 2 MS/s when analog channels are also sampled.

#### Input clock pacing

Analog, digital, and counter inputs can be sampled based on either an internal programmable input pacer or with an external clock source (**XAPCR** pin on the SCSI connector or the **EXT CLK** BNC connector). Analog channels can be paced from 0. 5 µs to 1000 seconds in 20.83 ns steps. Digital and counter inputs can be paced from 250 ns to 1 second in 20.83 ns steps.

The clock rate is 8 MHz maximum for both the internal pacer clock and external input scan clock.

#### **Output clock pacing**

Analog, digital, and timer operations can be paced using the internal output pacer clock (independent of the internal pacer clock), an external output pacer clock connected to the XDPCR pin on the SCSI connector, the internal programmable input pacer, or an external input pacing clock connected to either the XAPCR pin on the SCSI connector or the **EXT CLK** BNC connector.

The clock rate is 1 MHz maximum for analog output operations, and 8 MHz maximum for digital operations in which no analog channels are enabled.

### **Analog inputs**

The USB-1602HS-2AO has two single-ended analog inputs. Each input has a dedicated 16 bit A/D converter that provides true simultaneous sampling at rates of up to 2 MHz per channel. The input range is software selectable for  $\pm 10$  V,  $\pm 2.5$  V, or  $\pm 500$  mV.

You can pace analog input operations with the internal A/D pacer clock or with an external clock source. When using an external input scan clock, connect the clock source to the **XAPCR** pin on the SCSI connector or the **EXT CLK** BNC connector.

### Analog outputs

The USB-1602HS-2AO has two independent, 16-bit, analog output channels. The analog output range is -10V to +10V.

Each DAC channel can continuously output a waveform at up to 1 MHz. You can clock the DAC channels with the internal DAC scan clock or with an external DAC input clock. The internal analog input pacer clock can pace both the DAC output and the analog input simultaneously.

When using an external output scan clock, connect the clock source to the **XDPCR** pin on the SCSI connector or the **EXT CLK** BNC connector.

### Digital I/O

The USB-1602HS-2AO has 32 CMOS digital I/O lines configured as 16 digital inputs and 16 digital outputs. You can pace digital operations with the onboard scan clock or an external source. The maximum DIO transfer rate is 8 MS/s (software paced).

#### **Digital input scanning**

Digital input ports can be read synchronously along with analog channels in a scan, or asynchronously before, during, or after an analog input scan.

The digital inputs can sustain rates of up to 8 MS/s for one channel when no analog channels are sampled, and rates of up to 2 MS/s when analog channels are also sampled.

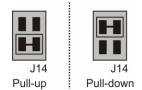

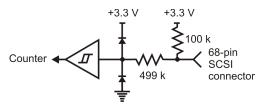

#### Internal pull-up/pull-down capability (J14)

Unconnected inputs are pulled high to +3.3V through 100 k resistors via a 4-pin jumper on the PCB board (**J14**). To configure these inputs to pull low (0 V), do the following:

**1.** Remove the 4 screws from the rear panel.

SCSI connector screws

Figure 8. Location of rear panel screws

2. Slide the board out of the housing and locate jumper J14.

Figure 9. Location of J14

- 3. Configure jumper J14 for either pull-up or pull-down configuration (refer to Figure 10).

- For pull-up, place the J14 shorting block across pins 1 and 2.

- For pull-down, place the J14 shorting block across pins 3 and 4.

Figure 10. J14 configuration

- 4. Slide the board into the housing.

- **5.** Replace the 4 screws on the rear panel.

#### Digital outputs and pattern generation

Digital outputs can be updated asynchronously at any time before, during, or after an acquisition. The USB-1602HS-2AO can generate a digital pattern at up to 4 MS/s.

Digital pattern generation is clocked with either the internal D/A scan clock or with an external D/A input clock. Digital patterns can be generated along with D/A waveforms. They are paced by the same selected clock. The on-board programmable clock generates updates ranging from once every 1000 seconds to 1 MHz, independent of the acquisition rate.

The digital outputs are driven low at power up and reset.

### Triggering

Triggering can be the most critical aspect of a data acquisition application. A trigger event occurs and data acquisition begins when specified conditions are met. You select the trigger mode and set up its parameters with software.

The USB-1602HS-2AO supports both hardware-based and software-based triggers. With a hardware-based trigger, an output value is compared in hardware to an input level on a specified channel. With software-based triggers, the analog, digital, and/or counter readings are checked by the PC in order to detect the trigger event.

The USB-1602HS-2AO supports the following trigger sources:

- Hardware-based triggers:

- Analog input hardware

- External digital trigger input

- Software-based triggers:

- Analog software trigger

- Digital pattern

- Counter/totalizer

#### Hardware-based triggering

With a hardware-based trigger, an output value is compared in hardware to an input level on a specified channel.

#### Analog input hardware

In this mode, the acquisition is triggered when a specified input level is achieved. The USB-1602HS-2AO uses true analog triggering in which the trigger level you program sets an analog DAC, which is then compared in hardware to the analog input level on the selected channel. This ensures an analog trigger latency that is less than  $1.5 \ \mu s$ .

You can select any analog channel as the trigger channel, but the selected channel must be the first channel in the scan. You can program the trigger level, the rising or falling edge, and hysteresis level. The trigger level can be any value within the voltage range for the selected trigger channel.

#### External digital trigger input

A separate digital trigger input line (**DIG TRIG**) allows TTL-level triggering with latencies guaranteed to be no less than 100 nS. The acquisition is triggered when a rising or falling edge is detected.

The trigger level is set at TTL sensitive. Latency is one sample period, maximum. The input signal range is  $\pm 15$  V. The trigger edge, logic level (1 or 0), and the rising or falling edge for the discrete trigger input are software selectable.

#### Software-based triggering

The three software-based trigger modes differ from hardware analog triggering and digital triggering because the analog, digital, or counter readings are checked by the PC in order to detect the trigger event.

#### Analog software

The acquisition is triggered when the computer issues a software command. You can select any analog channel in the scan as the trigger channel. The trigger level, the rising or falling edge, and hysteresis are software programmable. The trigger level can be any value within the range of the trigger channel. Latency is one sample period, maximum.

#### Digital pattern

The acquisition is triggered with a digital input channel pattern. You can select any scanned digital input channel pattern to trigger an acquisition, including the ability to mask or ignore specific bits.

You can program to trigger the conversion when equal to, not equal to, above, or below a value. Latency is one sample period, maximum.

#### Counter/Totalizer

The acquisition is triggered with the counter/totalize inputs. You can program triggering to occur on a frequency, or on total counts that are equal, not equal, above, below, or below a value, or that are within/outside of a window rising/falling edge. Latency is one sample period, maximum. You can select of the included counter channels as the trigger source.

Software-based triggering usually results in a long period of inactivity between the trigger condition being detected and the data being acquired. However, the USB-1602HS-2AO avoids this situation by using pre-trigger data. When software-based-triggering is used, and the PC detects the trigger condition — which may be thousands of readings after the actual occurrence of the signal — the USB-1602HS-2AO driver automatically looks back to the location in memory where the actual trigger-causing measurement occurred, and presents the acquired data that begins at the point where the trigger-causing measurement occurs. The maximum inactive period in this mode equals one scan period.

#### Set the trigger value > 0 when using a counter input as the trigger source

When using a counter for a trigger source, set the trigger value to 1 or greater. Since all counters start at zero with the first scan, there is no valid reference in regard to rising or falling edge. Setting the trigger value to 1 or greater ensures that a valid reference value is present, and that the first trigger will be legitimate.

#### Stop trigger modes

You can use any of the software trigger modes explained previously to stop an acquisition. For example, you can program an acquisition to begin on one event, such as a voltage level, and then stop on another event, such as a digital pattern.

#### Pre-triggering and post-triggering modes

The USB-1602HS-2AO supports four modes of pre-triggering and post-triggering. When using pre-trigger, you must use software-based triggering to initiate an acquisition.

#### No pre-trigger, post-trigger stop event

In this mode, data acquisition starts when the trigger is received, and the acquisition stops when the stop-trigger event is received.

#### Fixed pre-trigger with post-trigger stop event

In this mode, you set the number of pre-trigger readings to acquire. The acquisition continues until a stoptrigger event occurs.

#### No pre-trigger, infinite post-trigger

In this mode, no pre-trigger data is acquired. Instead, data is acquired beginning with the trigger event, and is terminated when you issue a command to halt the acquisition.

#### Fixed pre-trigger with infinite post-trigger

You set the amount of pre-trigger data to acquire. Then, the system continues to acquire data until the program issues a command to halt acquisition.

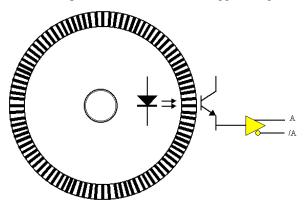

### **Counter inputs**

The USB-1602HS-2AO has four counters that can accept frequency inputs up to 20 MHz. The counter channels can be read as 16 or 32-bit counters. A counter can also be configured to be gated by one of the other counter inputs mapped as a gate input (refer to Mapped channels, on page 22). The input type is TTL, rising-edge triggered.

The counters can concurrently monitor time periods, frequencies, pulses, and other event driven incremental occurrences directly from pulse-generators, limit switches, proximity switches, and magnetic pick-ups.

Counter inputs can be read asynchronously under program control, or synchronously as part of an analog or digital scan group.

When reading synchronously, all counters are set to zero at the start of an acquisition. When reading asynchronously, counters may be cleared on each read, count up continually, or count until the 16-bit or 32-bit limit has been reached. See the counter mode descriptions below.

Figure 11. Typical USB-1602HS-2AO counter channel

#### **Mapped channels**

A *mapped channel* is one of four counter input signals (CTR0 to CTR3) that can get multiplexed into a counter module. The mapped channel can participate with the counter's input signal by gating the counter, latching the counter, and so on. The four possible choices for the mapped channel are the four counter input signals (post-debounce).

A mapped channel can be used to:

- gate the counter

- decrement the counter

- latch the current count to the count register

Usually, all counter outputs are latched at the beginning of each scan within the acquisition. However, you can use a second channel — known as the mapped channel — to latch the counter output.

#### Counter input modes

The USB-1602HS-2AO supports the following modes:

- Counter

- Period

- Pulse width measurement

- Timing

Program the counter operation mode with software.

#### Counter mode

A counter can be asynchronously read with or without *clear on read*. The asynchronous read-signals strobe when the lower 16-bits of the counter are read by software. The software can read the counter's high 16-bits some time later after reading the lower 16-bits. The full 32-bit result reflects the timing of the first asynchronous read strobe.

The following counter mode options are selectable with software.

| Counter mode     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Totalize         | <ul> <li>This mode allows the basic use of a 32-bit counter. The channel input increments the counter upward.</li> <li>When used as a 16-bit counter (counter low), one channel can be scanned up to an 8 MHz rate.</li> <li>When used as a 32-bit counter (counter high), two sample times are used to return the full 32-bit result. Therefore, a 32-bit counter can only be sampled at a 4 MHz maximum rate.</li> <li>The counter counts up and does not clear on every new sample. However, it does clear at the start of a new scan command. The counter rolls over on the 16-bit (counter low) boundary, or on the 32-bit (counter high) boundary.</li> </ul> |

| Clear on read    | The counter counts up and is cleared after each read. By default, the counter counts up and only clears the counter at the start of a new scan command. The value of the counter before it was cleared is latched and returned.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rollover         | The counter continues to count upward, rolling over on the 16 or 32-bit boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Stop at top      | The counter stops at the top of its count. The top of the count is FFFF hex (65,535) for the 16-bit mode, and FFFFFFFF hex (4,294,967,295) for the 32-bit mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16-bit or 32-bit | Sets the counter type to either 16-bits or 32-bits. The type of counter only matters if the counter is using the Stop at all FFFFs mode; otherwise, this option is ignored. The 16 bit mode requires less bandwidth for higher channels count and higher sample rates.                                                                                                                                                                                                                                                                                                                                                                                              |

#### Period mode

This mode allows for period measurement of the channel input.

You can measure x1, x10, x100 or x1000 periods, and 16-bit (counter low) or 32-bit (counter high) values. Four timebase, or tick-size, values are available (20.83 ns, 208.3 ns, 2.083  $\mu$ s, or 20.83  $\mu$ s). These values are based on the 48 MHz system clock. Any other channel can gate the period measurement. All period mode options are selectable with software.

#### Pulse width measurement mode

This mode is used to measure a channel's pulse width.

You can measure 16-bit or 32-bit values. Four timebase, or tick-size, values are available (20.83 ns, 208.3 ns, 2.083  $\mu$ s, or 20.83  $\mu$ s). These values are based on the 48 MHz system clock. Any other channel can gate the pulse width measurement. All pulse width options are selectable with software.

#### Timing mode

This mode is used to measure the time between two subsequent events, such as the edge of one channel with respect to the edge of another channel.

You can measure 16-bit or 32-bit values. Four timebase, or tick-size, values are available (20.83 ns, 208.3 ns, 2.083  $\mu$ s, or 20.83  $\mu$ s). All timing options are selectable with software.

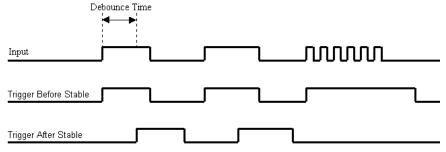

#### **Debounce function**

The USB-1602HS-2AO has debounce circuitry which eliminates switch-induced transients that are typically associated with electro-mechanical devices including relays, proximity switches, and encoders.

All debounce options are selectable with software. You can select a debounce time, debounce mode, and risingedge or falling-edge sensitivity.

Each channel's output can be debounced with 16 programmable debounce times in the range of 500 ns to 25.5 ms).

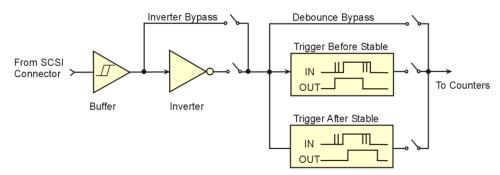

There are two debounce modes, as well as a debounce bypass, as shown in Figure 12. The signal from the buffer can be inverted before it enters the debounce circuitry. The inverter is used to make the input rising-edge or falling-edge sensitive.

Edge selection is available with or without debounce. In this case the debounce time setting is ignored and the input signal goes straight from the inverter or inverter bypass to the counter module.

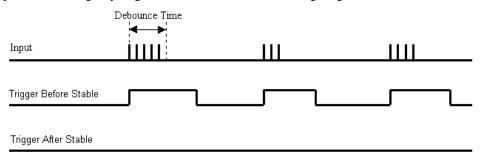

The two debounce modes are *trigger after stable* and *trigger before stable*. In either mode, the selected debounce time determines how fast the signal can change and still be recognized.

Figure 12. Debounce model block diagram

#### Trigger after stable mode

In the *trigger after stable* mode, the output of the debounce module does not change state until a period of stability has been achieved. This means that the input has an edge, and then must be stable for a period of time equal to the debounce time.

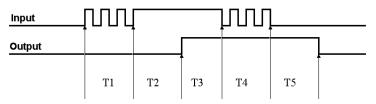

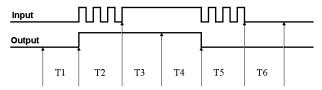

Figure 13. Debounce module – trigger after stable mode

T1 through T5 indicate time periods. In *trigger after stable* mode, the input signal to the debounce module is required to have a period of stability after an incoming edge, in order for that edge to be accepted (passed through to the counter module.) For this example, the debounce time is equal to T2 and T5.

- T1 In Figure 13, the input signal goes high at the beginning of time period T1, but never stays high for a period of time equal to the debounce time setting (equal to T2 for this example.)

- T2 At the end of time period T2, the input signal has transitioned high and stayed there for the required amount of time—therefore the output transitions high. If the input signal does not stabilize in the high state long enough, no transition would have appeared on the output and the entire disturbance on the input would have been rejected.

- T3 During time period T3, the input signal remained steady. No change in output is seen.

- T4 During time period T4, the input signal has more disturbances and does not stabilize in any state long enough. No change in the output is seen.

- T5 At the end of time period T5, the input signal has transitioned low and stayed there for the required amount of time—therefore the output goes low.

#### Trigger before stable mode

In the *trigger before stable* mode, the output of the debounce module immediately changes state, but will not change state again until a period of stability has passed. For this reason the mode can be used to detect glitches.

Figure 14. Debounce module – Trigger before stable mode

T1 through T5 indicate time periods.

T1 – In Figure 14, the input signal is low for the debounce time (equal to T1); therefore when the input edge arrives at the end of time period T1, it is accepted and the output (of the debounce module) goes high. Note that a period of stability must precede the edge in order for the edge to be accepted.

- T2 During time period T2, the input signal is not stable for a length of time equal to T1 (the debounce time setting for this example.) Therefore, the output stays "high" and does not change state during time period T2.

- T3 During time period T3, the input signal is stable for a time period equal to T1, meeting the debounce requirement. The output is held at the high state. This is the same state as the input.

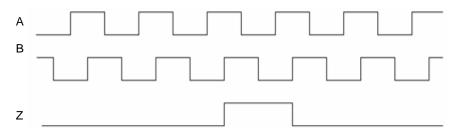

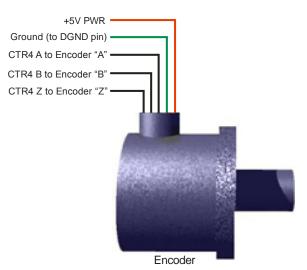

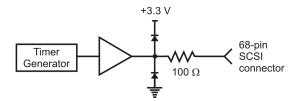

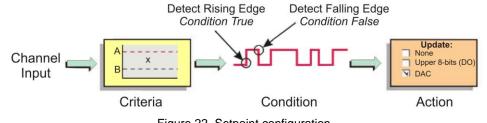

- T4 At anytime during time period T4, the input can change state. When this happens, the output will also change state. At the end of time period T4, the input changes state, going low, and the output follows this action [by going low].